# DIGITAL AMPLIFIER POWER STAGE

#### **Features**

- 2X12.5W at 10% THD+N into 8Ω BTL at 15V

- 2X8W at 10% THD+N into 8Ω BTL at 12V

- Support single-ended or differential input

- Over-temperature protection

- Over-current protection

- Under-voltage detection

- Error report and thermal warning

- Built-in anti-pop function for AD modulation

- PVDD range from 10.8V to 16.5V

- 24-pin E-TSSOP thermally-enhanced package

## **Applications**

- TV audio

- DVD Receiver

- Home Theaters

# **Description**

The AD9256 is a high efficiency stereo digital amplifier power stage delivering 85% efficiency. Devices need two power supplies for the AD9256 operation up to 15V supply for PVDD and 3.3V for VDD. The AD9256 can deliver 10W/CH output power into 8  $\Omega$  loudspeaker (in BTL operation) within 1% THD+N at supply 15V.

A built-in anti-pop function can reduce the speaker's pop without requiring complex anti-pop sequence in PWM input, when AD9256 is applied in AD modulation.

The AD9256 has included protection circuits that integrated on chip. Protections ensure the AD9256 against the fault conditions that could damage the AD9256. These safeguards of the AD9256 include over-temperature, over-current, and under-voltage protection circuits.

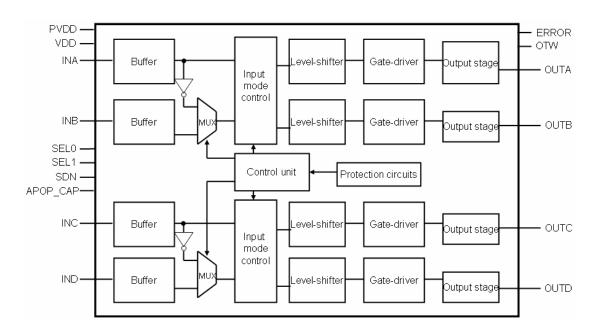

## **Functional Block Diagram**

Publication Date: Sep. 2009 Revision:0.1 1/15

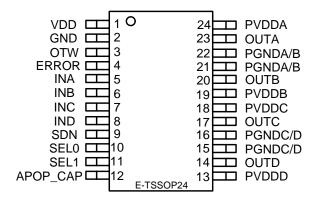

## **Pin Assignments**

# **Pin Description**

| PIN | NAME     | TYP | DESCRIPTION                                                       |

|-----|----------|-----|-------------------------------------------------------------------|

| 1   | VDD      | Р   | Power supply for digital circuit                                  |

| 2   | GND      | Р   | Ground for digital circuit                                        |

| 3   | OTW      | 0   | Over temperature warning.                                         |

| 4   | ERROR    | 0   | Error pointer                                                     |

| 5   | INA      | I   | PWM input A                                                       |

| 6   | INB      | I   | PWM input B                                                       |

| 7   | INC      | I   | PWM input C                                                       |

| 8   | IND      | I   | PWM input D                                                       |

| 9   | SDN      | I   | Shutdown (active-low) with soft pulled resistor 100kohm to ground |

| 10  | SEL0     | I   | Mode select pin 0                                                 |

| 11  | SEL1     | I   | Mode select pin 1                                                 |

| 12  | APOP_CAP | 0   | Anti-pop capacitor                                                |

| 13  | PVDDD    | Р   | Power supply for half bridge D                                    |

| 14  | OUTD     | 0   | Half-bridge output D                                              |

| 15  | PGNDC/D  | Р   | Ground for half bridge C/D                                        |

| 16  | PGNDC/D  | Р   | Ground for half bridge C/D                                        |

| 17  | OUTC     | 0   | Half-bridge output C                                              |

| 18  | PVDDC    | Р   | Power supply for half bridge C                                    |

| 19  | PVDDB    | Р   | Power supply for half bridge B                                    |

| 20  | OUTB     | 0   | Half-bridge output B                                              |

| 21  | PGNDA/B  | Р   | Ground for half bridge A/B                                        |

| 22  | PGNDA/B  | Р   | Ground for half bridge A/B                                        |

| 23  | OUTA     | 0   | Half-bridge output A                                              |

| 24  | PVDDA    | Р   | Power supply for half bridge A                                    |

Publication Date: Sep. 2009 Revision:0.1 **2/15**