ESMT EML3192

# 3A, 36V, 420kHz Non-synchronous Step-Down Converter

## **General Description**

The EML3192 is a 3A, current-mode step-down converter with an integrated high-side switch. The EML3192 operates with the wide input voltage from 4.5V to 36V and provides an adjustable output voltage from 0.808V to 30V. The EML3192 features a PWM mode operation with internally fixed 420kHz switching frequency. The EML3192 provides a single highly efficient solution with current mode control for fast loop response and easy compensation. The EML3192 also automatically enters PSM mode at light load.

Cycle-by-cycle current limiting and thermal shutdown are provided for fault condition protections. An internal 2ms soft-start design reduces input start-up current and prevents the output voltage and inductor current from overshooting during power-up.

The EML3192 requires a minimum number of external components and is available in E-SOP-8L with thermally enhanced package.

#### **Features**

- 4.5V to 36V Input Voltage Range

- 3A Continuous Output Current

- 100m\(\Omega\) Internal Power MOSFET Switch

- Output Adjustable from 0.808V

- Fixed 420kHz Switching Frequency

- Synchronize up to 1.5MHz

- Power Good Indicator

- Cycle-by-Cycle Current Limit, Frequency Fold

Back and thermal shutdown

- Stable with Low ESR Output Ceramic Capacitors

- 2ms Internal Soft-Start

- Thermally Enhanced E-SOP-8L Package

## **Applications**

- 12V and 24V Distributed Power Systems

- Battery Powered Systems

- Industrial Power Systems

- LCD and Plasma TVs

- Automotive System

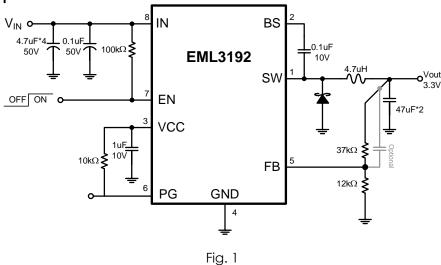

## **Typical Application**

Publication Date: Apr. 2016 Revision: 1.2 1/16

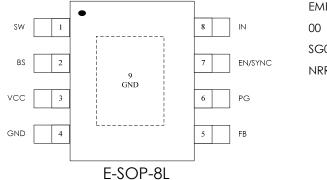

## **Package Configuration**

#### EML3192-00SG08NRR

00 Adjustable

SG08 E-SOP-8L Package

NRR RoHS & Halogen free package

Commercial Grade Temperature

Rating: -40 to 85°C

Package in Tape & Reel

Order, Mark & Packing information

| Package  | Vout(V)    | Product ID        | Marking                                               | Packing                 |

|----------|------------|-------------------|-------------------------------------------------------|-------------------------|

| E-SOP-8L | Adjustable | EML3192-00SG08NRR | ESMT EML3192 Tracking code  PINI DOT    1   2   3   4 | Tape & Reel<br>3K units |

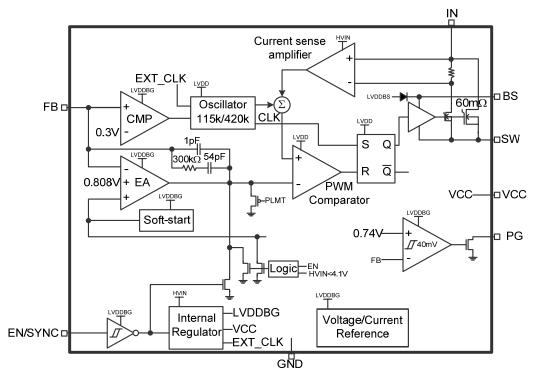

## **Functional Block Diagram**

Fig. 2

## **Pin Functions**

| Pin Name | E-SOP-8L | Function                                                                     |

|----------|----------|------------------------------------------------------------------------------|

|          |          | Switch Pin.                                                                  |

| SW       | 1        | Must be connected to Inductor. This pin connects to the drains of the        |

|          |          | internal main and synchronous power MOSFET switches.                         |

|          |          | Bootstrap.                                                                   |

| BS       | 2        | A 10nF or greater capacitor must be connected from this pin to SW. It        |

|          |          | can boost the gate drive to fully turn on the internal high side NMOS.       |

| vcc      | 3        | Bias Supply                                                                  |

| VCC      | 3        | Decouple this pin with a 1uF capacitor                                       |

| GND      | 4        | Ground Pin.                                                                  |

|          |          | Feedback Pin.                                                                |

| FB       | 5        | Receives the feedback voltage from an external resistive divider             |

|          |          | across the output, it regulates at 0.808V.                                   |

| PG       | 6        | Power Good Indicator.                                                        |

| rg 0     |          | Connect this pin to Vcc or Vout by a $100 \text{K}\Omega$ pull-up resistor.  |

|          |          | Enable Pin.                                                                  |

| EN/SYNC  | 7        | This pin provides a digital control to turn the converter on or off.         |

|          |          | Connect to $V_{IN}$ with a $100 K\Omega$ resistor for self-startup.          |

|          | 8        | Power Input Pin.                                                             |

| IN       |          | Drive 4.5V to 36V voltage to this pin to power on this chip. Connecting      |

| IIV      |          | a 10uF ceramic bypass capacitor between V <sub>IN</sub> and GND to eliminate |

|          |          | noise.                                                                       |

|          |          | Ground Pin/Thermal Pad                                                       |

| GND      | 9        | This Pin must be connected to ground. The thermal pad with large             |

|          |          | thermal land area on the PCB will helpful chip power dissipation.            |

Publication Date: Apr. 2016

Revision: 1.2 3/16

## **Absolute Maximum Ratings**

Devices are subjected to fail if they stay above absolute maximum ratings.

| Input Voltage (IN)                    | -0.3V to +42V |

|---------------------------------------|---------------|

| Switch Voltage (SW) 0.3               | V to Vin+0.3V |

| Boost Voltage (BS) V <sub>sw</sub> -0 | .3V to Vsw+6V |

| Enable Voltage (EN)                   | -0.3V to Vin  |

| All Other Pins (VCC, FB, PG)          | -0.3V to +6V  |

| Lead Temperature (Soldering, 10 sec)  | 260°C         |

## Thermal data

| Package  | Thermal resistance   | Parameter                          | Value  |

|----------|----------------------|------------------------------------|--------|

|          | heta JA (Note 2)     | Junction-to-ambient                | 50°C/W |

| E-SOP-8L | heta л (Note 3)      | Junction-to-top surface of package | 39°C/W |

|          | $\theta$ JC (Note 4) | Junction-to-case                   | 10°C/W |

## **Electrical Characteristics**

VIN=12V, T<sub>A</sub>=+25°C, unless otherwise specified.

| Symbol                      | Parameter                           | Conditions                               | Min   | Тур   | Max   | Units                  |

|-----------------------------|-------------------------------------|------------------------------------------|-------|-------|-------|------------------------|

| $V_{\text{FB}}$             | Feedback Voltage                    | 4.5V≦V <sub>IN</sub> ≦36V                | 0.788 | 0.808 | 0.828 | ٧                      |

| I <sub>FB</sub>             | Feedback Current                    | V <sub>FB</sub> =0.8V                    |       | 1     |       | nA                     |

| R <sub>DS(ON)</sub>         | Switch on Resistance                |                                          |       | 100   | 150   | mΩ                     |

| Isw                         | High-side Switch Leakage            | V <sub>EN</sub> =0V, V <sub>SW</sub> =0V |       |       | 10    | μΑ                     |

| I <sub>LIM</sub>            | Current Limit                       |                                          |       | 6.8   |       | Α                      |

|                             | Oscillation Frequency               | V <sub>FB</sub> =0.6V                    | 240   | 420   | 600   | kHz                    |

| f <sub>osc</sub>            | Fold-Back Frequency                 | V <sub>FB</sub> =0V                      | 25    | 115   | 205   | kHz                    |

| Ton                         | Minimum On Time (note5)             |                                          |       | 100   |       | ns                     |

| Toff                        | Minimum Off Time (note5)            |                                          |       | 200   |       | ns                     |

| $V_{UVLO}$                  | Under Voltage Lock Out              | Rising                                   | 3.9   | 4.2   | 4.5   | V                      |

| <b>V</b> UVLO               | Under Voltage Lock Out Hysteresis   |                                          |       | 800   |       | mV                     |

|                             | EN Input Low Voltage                |                                          |       |       | 0.4   | V                      |

|                             | EN Input High Voltage               |                                          | 1.5   |       |       | <b>V</b>               |

| For other house of Commont  | Fig. wild. I have the Column in the | V <sub>EN</sub> =2V                      |       | -5    |       | μΑ                     |

| I <sub>EN</sub>             | Enable Input Current                | V <sub>EN</sub> =0V                      |       | -1    |       | μΑ                     |

| г                           | Sync Frequency Range(Low)           |                                          |       | 300   |       | kHz                    |

| F <sub>SYNCL</sub>          | Sync Frequency Range(High)          |                                          |       | 1.5   |       | MHz                    |

| $T_{\text{EN,Low}}$         | Enable Turn OFF                     |                                          |       | 5     |       | μs                     |

| $T_{SD}$                    | Thermal Shutdown                    |                                          |       | 150   |       | $^{\circ}\!\mathbb{C}$ |

| Thermal Shutdown Hysteresis |                                     |                                          |       | 20    |       | $^{\circ}\!\mathbb{C}$ |

| Supply Current ( Shutdown ) |                                     | V <sub>EN</sub> =0                       |       | 8     |       | υA                     |

|                             | Supply Current( Quiescent)          | V <sub>EN</sub> =2V,V <sub>FB</sub> =1V  |       | 0.5   | 1.0   | mA                     |

|                             | Power Good Threshold Rising         |                                          | 0.69  | 0.74  | 0.79  | V                      |

|                             | Power Good Threshold Hysteresis     |                                          |       | 40    |       | mV                     |

| $V_{PG}$                    | Power Good Pin level                | PG Sink 4mA                              |       |       | 0.4   | ٧                      |

Revision: 1.2 4/16

- Note 1:  $T_{J}$  is a function of the ambient temperature  $T_{A}$  and power dissipation  $P_{D}$  ( $T_{J} = T_{A} + (P_{D}) * \theta_{JA}$ )).

- Note 2:  $\theta_{\text{JA}}$  is simulated in the natural convection at  $T_A=25^{\circ}\text{C}$  on a highly effective thermal conductivity (thermal land area completed with >3x3cm² area) board (2 layers , 2SOP ) according to the JEDEC 51-7 thermal measurement standard.

- **Note 3:**  $\theta$  in represents the heat resistance between the chip junction and the top surface of package.

- Note 4:  $\theta_{JC}$  represents the heat resistance between the chip junction and the center of the exposed pad on the underside of the package.

Publication Date: Apr. 2016 Revision: 1.2 5/16

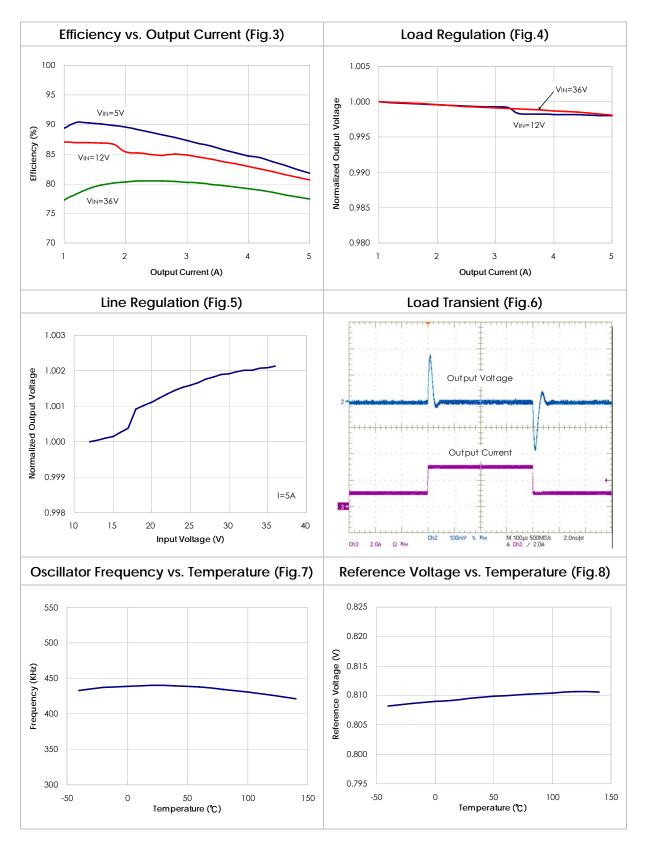

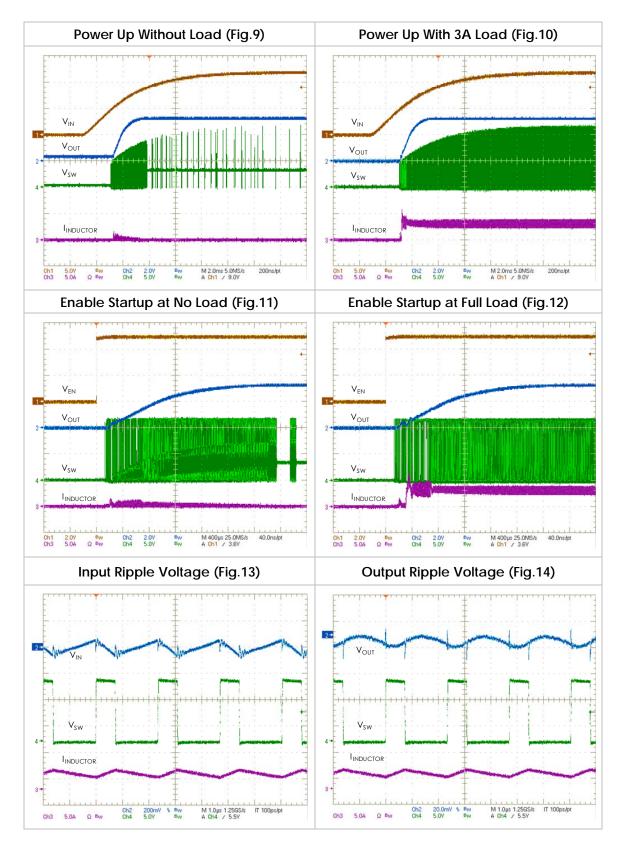

## **Typical Performance Characteristics**

$V_{\text{IN}} = 12 V, \, V_{\text{OUT}} = 3.3 V, \, T_{\text{A}} = 25 \, ^{\circ}\!\!\!\! \text{C}$  , unless otherwise specified.

Publication Date: Apr. 2016 Revision: 1.2 6/16

## **Typical Performance Characteristics**

$V_{\text{IN}} = 12 V, \, V_{\text{OUT}} = 3.3 V, \, T_{\text{A}} = 25 \, ^{\circ}\!\!\! \text{C}$  , unless otherwise specified.

### **Detailed Description**

The EML3192 is a constant-frequency, current mode, automotive buck converter with an integrated high-side switch. The device operates with input voltages from 4.5V to 36V and tolerates input transients up to 42V. During light-load conditions, the device enters PSM automatically.

#### Wide Input Voltage Range (4.5V to 36V)

The EML3192 includes two separate supply inputs, IN and BS, specified for a wide 4.5V to 36V input voltage range. IN provides power to the device and BS provides power to the internal high-side switch driver.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage with the internal 0.808V reference and outputs a current proportional to the difference between the two. This output current is then used to charge or discharge the internal compensation network to form the COMP voltage, which is used to control the power MOSFET current. The optimized internal compensation network minimizes the external component counts and simplifies the control loop design.

#### **Internal Regulator**

The EML3192 includes a 5V linear regulator, VCC, which provides power to the internal circuitry. Connect a 1uF capacitor from VCC to GND to bypass the internal LDO. Loading on this LDO is not recommended.

#### **Power Good Indicator**

Typically, a  $100k\Omega$  resistor connected between VCC or Vout and PG pin is recommended. When the FB is below 0.70V, the PG pin will be internally pulled low. When the FB is above 0.74V, The PG becomes an open-drain output.

#### Minimum On-Time

The device features a 100ns minimum on-time that ensures proper operation at 420kHz switching frequency and high differential voltage between the input and the output.

#### Enable/Sync Control

The EML3192 has a dedicated Enable/SYNC control pin. By pulling it high or low, that can be enabled and disabled. Tie EN to IN through a 100k $\Omega$  resistor for automatic start up. To disable the part, EN must be pulled low for at least 5us.

When floating, EN is pulled up to about 2.0V by an internal 1uA current source so it is enabled. To pull it down, 1uA current capability is needed.

The EML3192 can also be synchronized to external clock range from 300kHz up to 1.5MHz through the EN/SYNC pin.

The internal clock rising edge is synchronized to the external clock rising edge.

#### Over-Temperature protection

Thermal overload protection limits the total power dissipation in the device. When the junction temperature exceeds  $150^{\circ}$ C, an internal thermal sensor shuts down the whole chip. The thermal sensor turns on the IC again after the junction temperature is cooled by  $10^{\circ}$ C

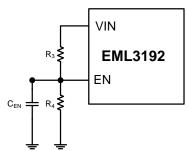

#### **Under Voltage Lock-out (UVLO)**

UVLO is implemented to protect the chip from operating at insufficient supply voltage. The UVLO rising threshold is about 4.2V while its falling threshold is about 3.4V. If a higher UVLO is required for a specified application, as the EN pin shown in Fig.16 below to adjust input voltage UVLO via two external resistors and a filter capacitor. For example, choosing  $R_3\!=\!560k$  and  $R_4\!=\!62k$ , the  $V_{\text{start}}$  and  $V_{\text{stop}}$  would be around 10V and 7V. The EN enable threshold is around 1.0V, and with 100mV hysteresis window for shutdown.

Fig.15 Two external resistors on EN pin

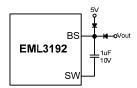

#### **Boost Capacitor**

Connect a 1uF capacitor between the BS pin and SW pin. This capacitor provides the gate driver voltage for the high-side MOSFET. Also, an UVLO in the floating supply is implemented to protect the high-side MOSFET and its driver from operating at insufficient supply voltage. The UVLO rising threshold is about 2.2V while its hysteresis is about 0.16V.

#### Over-Current protection

Over-current limiting is implemented by sensing the drain-to-source voltage across the high-side MOSFET. The drain to source voltage is then compared to a voltage level representing the over-current threshold limit. If the drain-to-source voltage exceeds the over-current threshold limit, the over-current indicator is set true. Once over-current indicator is set true, over-current limiting is triggered. The high-side MOSFET is turned off for the rest of the cycle. The output voltage will start to drop if the output is dead-short to ground, suddenly. Once the FB is lower than 0.3V, the EML3192 is restarted periodically till the dead-short event is removed.

Publication Date: Apr. 2016 Revision: 1.2 8/16

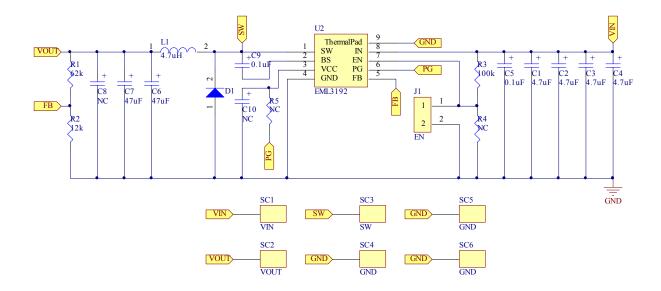

## **Application Information**

The schematic on the front page shows a typical application circuit. The EML3192 can provide up to 3A output current at a 3.3V output voltage. For proper thermal performances, the exposed pad of the device must be soldered down to the PCB. With the optimized internal compensation network, minimize the external component counts and simplify the control loop design.

#### **Setting the Output Voltage**

The external resistor divider is not only used to set the output voltage, but also sets the system loop bandwidth with the internal compensation capacitor. The R1 should be chosen around  $40.2 k\Omega$  for better transient performance, and the R2 is then derived by:

$$R_2 = R_1 \times \frac{0.808V}{V_{OUT} - 0.808V}$$

Table1-Resistor Selection for Common Output Voltages

| Vout | R1 (kΩ)   | R2 (kΩ) |

|------|-----------|---------|

| 1.8V | 33.1 (1%) | 27 (1%) |

| 2.5V | 50.3 (1%) | 24 (1%) |

| 3.3V | 37 (1%)   | 12 (1%) |

| 5.0V | 62.3 (1%) | 12 (1%) |

#### Selecting the Inductor

The common rule for determining the inductance to use is to allow the peak-to-peak ripple current in the inductor to be between 20% and 40% of the DC maximum load current, typical 30%. And also have sufficiently high saturation current rating and a DCR as low as possible. Generally, it is desirable to have lower inductance in switching power supplies, because it usually corresponding to faster transient response, smaller DCR and reduced size for more compact designs. But too low of an inductance results in higher ripple current such that over-current protection at full load could be falsely triggered. Also, the output ripple voltage and efficiency become worse with lower inductance. Under light load condition, like below 100mA, larger inductance is recommended for improved efficiency. The inductance and its peak current could be calculated by:

$$L = \frac{V_{OUT}}{f_S \times \Delta I_I} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

$$I_{LP} = I_{LOAD} + \frac{\Delta I_L}{2} = I_{LOAD} + \frac{V_{OUT}}{2 \times f_S \times L} \cdot \left(1 - \frac{V_{OUT}}{V_{|N}}\right)$$

Which  $f_{\text{S}}$  is the switching frequency;  $I_{\text{LOAD}}$  is the load current.

#### Selecting the Input capacitor

The input current to the step-down converter is

discontinuous, therefore a capacitor is required to supply the AC current for step-down converter to maintain the DC input voltage. Use low ESR capacitor for the best performance. The high frequency impedance of the capacitor should be lower than the input source impedance for bypassing the high frequency switching current locally. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. To prevent excessive voltage ripple at input, the relationship between the input ripple and the capacitance could be estimated by:

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_{S} \times C_{1}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

#### Selecting the Diode

The diode connected between SW and GND is the path for the inductor current during the high-side MOSFET turns off. Choose the diode with minimum forward voltage drop and recovery time, like Schottky. And, the reverse voltage rating is greater than maximum input voltage and whose current rating is greater than the maximum load current.

**Table2-Diode Selection Guide**

| Diode | Voltage/Current<br>Rating | Manufacture |

|-------|---------------------------|-------------|

| B540C | 40V, 5A                   | Diodes Inc. |

#### Selecting the Output capacitor

The output capacitor (C2) is required to maintain the DC output voltage, keeps the output ripple small, and ensures regulation loop stability. The lower ESR capacitors are preferred to keep lower output ripple. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times f_S \times C_2}\right)$$

Which L is the inductance and  $R_{ESR}$  is the equivalent series resistance (ESR) of the output capacitor.

In case of lower ESR capacitor adopted, the output ripple is mainly caused by the capacitance and the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_S^2 \times L \times C_2} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Or, the ESR dominates the impedance at switching frequency. After simplification, the output voltage ripple can approximated to

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The characteristics of the output capacitor also affect the loop stability of regulation system. Low ESR ceramic capacitors with X5R or X7R dielectrics are recommended.

#### **External Bootstrap Diode**

An external bootstrap diode is recommended to add between external 5V and BS pin to enhance efficiency of the regulator. The external 5V can be a 5V fixed input from system or a 5V output of the EML3192. The low cost diode, like 1N4148, is sufficient.

With such diode, 5V input voltage can output 3.3V and 2.5V with just 30mA load.

# **Applications**

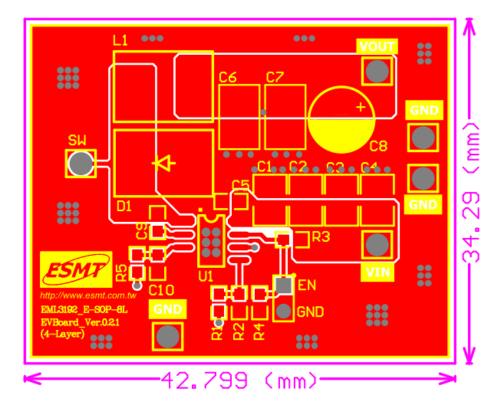

# Typical schematic for PCB layout

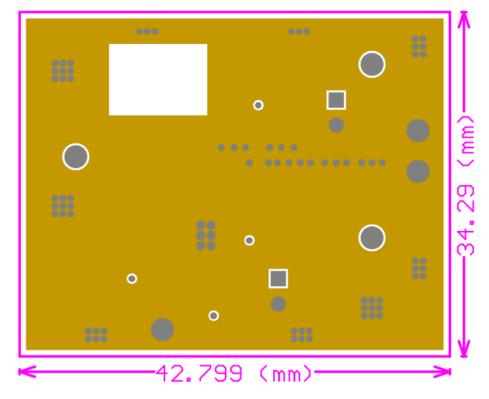

# Typical schematic for PCB layout (cont.)

Top-side Layout

Layer 2 Layout

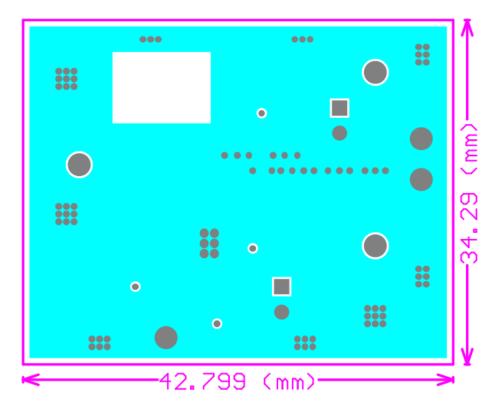

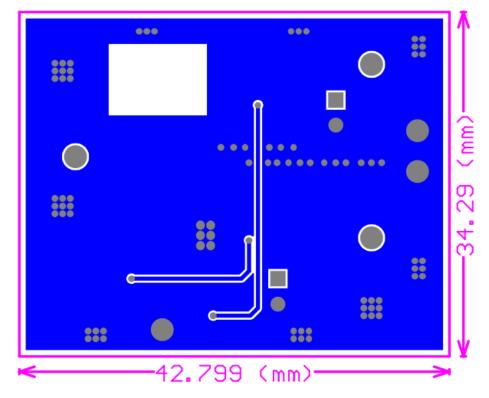

# Typical schematic for PCB layout (cont.)

Layer 3 Layout

Bottom-side Layout

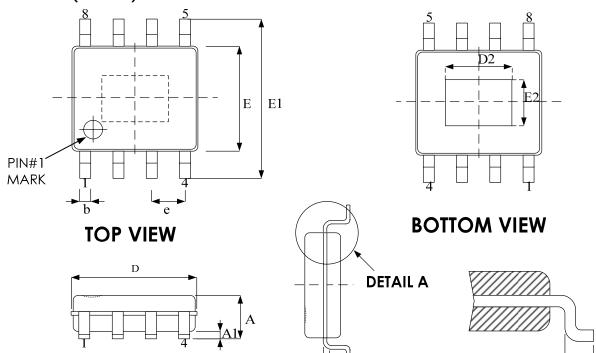

# Package Outline Drawing E-SOP-8L (150 mil)

| Crunala o 1 | Dimension in mm |      |  |

|-------------|-----------------|------|--|

| Symbol      | Min             | Max  |  |

| А           | 1.35            | 1.75 |  |

| A1          | 0.00            | 0.25 |  |

| Ъ           | 0.33            | 0.51 |  |

| С           | 0.17            | 0.25 |  |

| D           | 4.80            | 5.00 |  |

| Е           | 3.81            | 4.00 |  |

| E1          | 5.79            | 6.20 |  |

| е           | 1.27 BSC        |      |  |

| L           | 0.41            | 1.27 |  |

**SIDE VIEW**

Exposed pad

|    | Dimension in mm |      |  |

|----|-----------------|------|--|

|    | Min             | Max  |  |

| D2 | 1.93            | 2.39 |  |

| E2 | 1.93            | 2.39 |  |

**DETAIL A**

# **Revision History**

| Revision | Date       | Description                                                                                                                                                             |  |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.1      | 2015.12.10 | Initial version.                                                                                                                                                        |  |

| 1.0      | 2015.12.31 | Remove preliminary word and modify version to 1.0                                                                                                                       |  |

| 1.1      | 2016.02.05 | Modified the Absolute Maximum Ratings.                                                                                                                                  |  |

| 1.2      | 2016.04.18 | Updated the typical application circuit.     Updated the functional block diagram.     Updated the detailed description of UVLO control.     Updated the PCB schematic. |  |

ESMT EML3192

## Important Notice

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Apr. 2016 Revision: 1.2 16/16