# 2-Vrms Cap-Less Line Driver with Adjustable Gain

#### Features

- Operation Voltage: 3.0V to 3.6V

- Cap-less Output

- Eliminates Output Capacitors

- Improves Low Frequency Response

- Reduces POP/Clicks

- Reduce Board Area and Component Cost

- Low Noise and THD

- Typical SNR 107dB

- Typical Vn 7uVrms

- Typical THD+N < 0.02%

- Maximum Output Voltage Swing into 10kΩ Load

2Vrms at 3.3V Supply Voltage

- 600Ω Output Load Compliant

- Differential Input, single-Ended Output

- External Gain Setting from 1V/V to 10V/V

- Fast Start-up Time : 0.5ms

- Integrated De-Pop Control

- External Under Voltage Protection

- Thermal Protection

- Active Mute Control for Pop-less Audio ON/OFF Control

- +/-8kV IEC ESD Protection at line outputs

#### Applications

- LCD / PDP TVs

- CD / DVD players

- Set-Top Boxes

- Home Theater in Box

### Description

The AD22653B is a 2-Vrms cap-less stereo line driver. The device is ideal for single supply electronics. Cap-less design can eliminate output dc-blocking capacitors for better low frequency response and save cost.

The AD22653B is capable of delivering 2-Vrms output into a  $10k\Omega$  load with 3.3V supply. The gain settings can be set by users from  $\pm 1V/V$  to  $\pm 10V/V$  externally, and gain can be configured individually for R/L channel. The AD22653B has built-in active-mute control for pop-less audio on/off control. The AD22653B has internal and external under voltage protection to prevent POP noise. Built-in de-pop control sequence also help AD22653B to be a pop-less device.

The AD22653B is available in a 14-pin TSSOP package.

#### Ordering Information

| Product ID       | Package  | Packing                | Comments   |

|------------------|----------|------------------------|------------|

| AD22653B-QH14NAT | TSSOP-14 | 96 Units / Tube        |            |

|                  |          | 100 Tubes / Small Box  | Green (HF) |

| AD22653B-QH14NAR |          | 2.5k Units Tape & Reel |            |

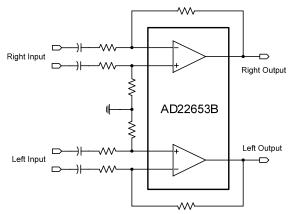

## **Simplified Application Circuit**

Elite Semiconductor Memory Technology Inc.

Publication Date: Feb. 2016 Revision: 1.1 1/19

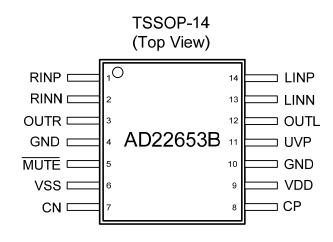

## **Pin Assignments**

#### **Pin Description**

| No. | Name | Type <sup>(1)</sup> | Pin Description                                        |

|-----|------|---------------------|--------------------------------------------------------|

| 1   | RINP | I                   | Right channel OP positive input                        |

| 2   | RINN | I                   | Right channel OP negative input                        |

| 3   | OUTR | 0                   | Right channel OP output                                |

| 4   | SGND | Р                   | Signal ground                                          |

| 5   | MUTE | Ι                   | Mute, active low                                       |

| 6   | PVSS | Р                   | Supply voltage                                         |

| 7   | CN   | I/O                 | Charge-pump flying capacitor negative terminal         |

| 8   | СР   | I/O                 | Charge-pump flying capacitor positive terminal         |

| 9   | PVDD | Р                   | Positive supply                                        |

| 10  | PGND | Р                   | Power ground                                           |

| 11  | UVP  | Ι                   | Under-voltage protection input, internally pulled high |

| 12  | OUTL | 0                   | Left channel OP output                                 |

| 13  | LINN | I                   | Left channel OP negative input                         |

| 14  | LINP | I                   | Left channel OP positive input                         |

(1) I=input, O=output, P=power

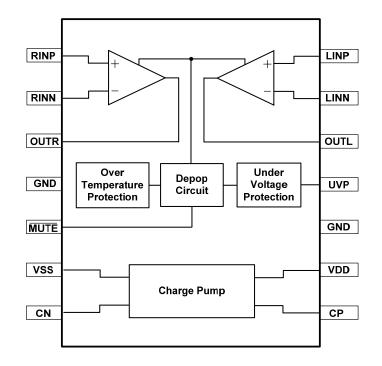

# **Functional Block Diagram**

### **Available Package**

| Package Type | Device No. | <i>⊖</i> <sub>ja</sub> (°C/W) <sup>(1)</sup> | <i>Θ</i> <sub>jc</sub> (℃/₩) <sup>(2)</sup> |

|--------------|------------|----------------------------------------------|---------------------------------------------|

| TSSOP-14     | AD22653B   | 100                                          | 32                                          |

(1)  $\theta_{ja}$  is measured at room temperature (TA=25°C), natural convection environment test board, which is constructed with a thermal efficient,

2-layers PCB. The measurement is tested using the JEDEC51-3 thermal measurement standard.

(2)  $\Theta_{jc}$  represents the heat resistance for the heat flow between the chip and package's top surface.

# **Marking Information**

AD22653B Line 1 : LOGO Line 2 : Product No. Line 3 : Tracking Code