# 2x40W Stereo / 1x80W Mono Class-D Audio Amplifier With Power Limit

#### **Features**

- Single supply voltage

4.5V ~ 26V for loudspeaker driver

Built-in LDO output 5V for others

- Supports Multiple Output Configurations BTL Mode: 30W/CH into  $8\Omega$  at 24 V BTL Mode: 40W/CH into  $4\Omega$  at 19 V PBTL Mode: 60W/CH into  $4\Omega$  at 24 V PBTL Mode: 80W/CH into  $2\Omega$  at 20 V

- Loudspeaker performance

- BTL Mode: 30W/CH into  $8\Omega$  <1% THD+N@24V BTL Mode: 40W/CH into  $4\Omega$  <1% THD+N@19V

- >90% efficient Class-D operation eliminates need for heat sink

- Differential inputs

- Four selectable, fixed gain settings

- Internal oscillator

- Short-Circuit protection with auto recovery option

- Under-Voltage detection

- Over-Voltage protection

- Pop noise and click noise reduction

- Adjustable power limit function for speaker protection

- Output DC detection for speaker protection

- Over temperature protection with auto recovery

- E-TSSOP 28L Epad-Up thermally enhanced package

#### **Applications**

- TV audio

- Boom-Box

- Powered speaker

- Monitors

- Consumer Audio Equipment

#### **Description**

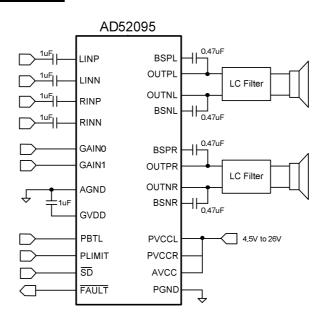

The AD52095 is a high efficiency stereo class-D audio amplifier with adjustable power limit function. The loudspeaker driver operates from 4.5V~26V supply voltage and analog circuit operates at 5V supply voltage. It can deliver 40W/CH output power into  $4\Omega$  or  $8\Omega$  loudspeaker within 1% THD+N at 24V supply voltage.

AD52095 provides parallel BTL (Mono) application, and it can deliver 80W into  $2\Omega$  loudspeaker at 24V supply voltage. The adjustable power limit function allows user to set a voltage rail lower than half of 5V to limit the amount of current through the speaker.

Output DC detection prevents speaker damage from long-time current stress. AD52095 output short circuit and over temperature protection include auto-recovery feature.

#### **Simplified Application Circuit**

Publication Date: Mar. 2022 Revision: 0.1 1/25

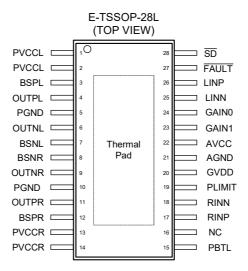

## **Pin Assignments**

# **Pin Description**

| NAME   | E-TSSOP<br>-28L | TYP | DESCRIPTION                                                                                                                                                                                                  |  |  |  |

|--------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PVCCL  | 1,2             | Р   | High-voltage power supply for right-channel. Right channel and left channel power supply inputs are connect internal.                                                                                        |  |  |  |

| BSPL   | 3               | ı   | Bootstrap I/O for left channel, positive high side FET.                                                                                                                                                      |  |  |  |

| OUTPL  | 4               | 0   | Class-D H-bridge positive output for left channel.                                                                                                                                                           |  |  |  |

| PGND   | 5               | Р   | Power ground for the H-bridges.                                                                                                                                                                              |  |  |  |

| OUTNL  | 6               | 0   | Class-D H-bridge negative output for left channel.                                                                                                                                                           |  |  |  |

| BSNL   | 7               | ı   | Bootstrap I/O for left channel, negative high side FET.                                                                                                                                                      |  |  |  |

| BSNR   | 8               | I   | Bootstrap I/O for right channel, negative high side FET.                                                                                                                                                     |  |  |  |

| OUTNR  | 9               | 0   | Class-D H-bridge negative output for right channel.                                                                                                                                                          |  |  |  |

| PGND   | 10              | Р   | Power ground for the H-bridges.                                                                                                                                                                              |  |  |  |

| OUTPR  | 11              | 0   | Class-D H-bridge positive output for right channel.                                                                                                                                                          |  |  |  |

| BSPR   | 12              | I   | Bootstrap I/O for right channel, positive high side FET.                                                                                                                                                     |  |  |  |

| PVCCR  | 13,14           | Р   | High-voltage power supply for right-channel. Right channel and left channel power supply inputs are connect internal.                                                                                        |  |  |  |

| PBTL   | 15              | I   | Parallel BTL mode switch, high for parallel BTL output. Voltage compliance to AVCC.                                                                                                                          |  |  |  |

| NC     | 16              | NA  | NC pin.                                                                                                                                                                                                      |  |  |  |

| RINP   | 17              | I   | Positive audio input for right channel, biased at 1/10 of PVCC supply voltage.                                                                                                                               |  |  |  |

| RINN   | 18              | I   | Negative audio input for right channel, biased at 1/10 of PVCC supply voltage.                                                                                                                               |  |  |  |

| PLIMIT | 19              | ı   | Power limit level adjustment. Connect a resistor divider from GVDD to GND to set power limit. Give V(PLIMIT) <2.4V to set power limit level. Connect to GVDD (>2.4V) or GND to disable power limit function. |  |  |  |

| GVDD   | 20              | 0   | 5V regulated output, also used as supply for PLIMIT function.                                                                                                                                                |  |  |  |

Elite Semiconductor Microelectronics Technology Inc.

Publication Date: Mar. 2022 Revision: 0.1 **2/25**

| AGND        | 21 | Р | Analog signal ground.                                                                                                                              |  |

|-------------|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AVCC        | 22 | Р | Analog supply.                                                                                                                                     |  |

| GAIN1       | 23 | I | Gain select most significant bit, voltage compliance to AVCC.                                                                                      |  |

| GAIN0       | 24 | I | Gain select least significant bit, voltage compliance to AVCC.                                                                                     |  |

| LINN        | 25 | 1 | Negative audio input for left channel, biased at 1/10 of PVCC supply voltage.                                                                      |  |

| LINP        | 26 | 1 | Positive audio input for left channel, biased at 1/10 of PVCC supply voltage.                                                                      |  |

| FAULT       | 27 | 0 | Open drain output used to display short circuit or dc detect fault, voltage compliant to AVCC. Short circuit faults can be set to auto-recovery by |  |

|             |    |   | connecting $\overline{FAULT}$ pin to $\overline{SD}$ pin. Otherwise, both short circuit faults and dc detect faults must be reset by cycling AVCC. |  |

| SD          | 28 | I | Shutdown signal for IC (low = disabled, high = operational), voltage compliance to AVCC.                                                           |  |

| Thermal Pad |    | Р | Must be good connected to heat-sink for power dissipation requirement.                                                                             |  |

### **Ordering Information**

| Product ID      | Package                  | Packing                                  | Comments |

|-----------------|--------------------------|------------------------------------------|----------|

| AD52095-QG28NRR | E-TSSOP 28L<br>(Epad-Up) | 2500 Units / Reel<br>1 Reels / Small Box | Green    |

## Available Package

| Package Type | Device No. | θ <sub>JA</sub> (°C/W) | Ψлт(°С/ <b>W</b> ) | Exposed Thermal Pad |

|--------------|------------|------------------------|--------------------|---------------------|

| E-TSSOP 28L  | AD52095    | 10                     | 1.2                | Yes (Note 1)        |

| (Epad-Up)    | AD52095    |                        |                    |                     |

- Note 1.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB's ground plane is necessary.

- Note 1.2:  $\theta_{JA}$  is simulated on a room temperature ( $T_A$ =25 $^{\circ}$ C), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is simulated using the JEDEC51-5 thermal measurement standard.

- Note 1.3:  $\Psi_{JT}$  represents the thermal parameter for the heat flow between the chip junction and the package's top surface center. It's extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-5.

Publication Date: Mar. 2022 Revision: 0.1 3/25