# 2x20W Stereo / 1x40W Mono Digital Audio Amplifier With 24 Bands EQ Functions

#### **Features**

- 16/18/20/24-bits input with I<sup>2</sup>S, Left-alignment and Right-alignment data format

- PSNR & DR (A-weighting)

Loudspeaker: 102dB (PSNR), 108dB (DR)

@24V

- Multiple sampling frequencies (Fs)

32kHz / 44.1kHz / 48kHz and

64kHz / 88.2kHz / 96kHz and

128kHz / 176.4kHz / 192kHz

- I<sup>2</sup>C control interface

- Channel mixing

- Volume control (+12dB ~ -103dB, 0.125dB/step)

- Power clipping function

- DRC and DTC function

- 24 bands parametric speaker EQ

- Bass/Treble tone control

- DRC and post scale boost

- Check-sum coefficient protection

- Noise gate function

- Pop noise less muting (Quick Mute/Quick Start)

- Sleep function

- X3 over sampling for 32kHz FS

- AM interference frequency switching

- Level meter

- Post-scale and DRC offset volume support

- Over current protection function (OCP)

- Over temperature protection function (OTP)

- Under voltage lock out (UVLO)

- Over voltage protection function (OVP)

- DC detection function (DCDET)

- Clock detection function (CKDET)

- Lead-free E-LQFP-48L

#### **Applications**

- TV audio

- Boom-box, CD and DVD receiver, docking system

- Powered speaker

- Wireless audio

### **Description**

AD82589 is an integrated audio system solution, embedding digital audio processing power stage amplifier.

AD82589 has a programmable slew-rate controlled output buffer, which drives one (mono) or two (stereo) speakers directly. In addition, it is insusceptible to supply voltage fluctuation due to the close-loop design.

AD82589 can provide advanced audio processing capabilities, such as volume control, 24 bands EQ, audio mixing and Dynamic Range Control (DRC). These functions are fully programmable via a simple  $I^2C$  interface.

Robust protection circuits are provided to protect AD82589 from damage due to accidental erroneous operation. AD82589, being a digital circuit design, is more tolerant to noise and PVT (Process, Voltage, and Temperature) variation than the analog Class-AB or Class-D audio amplifier counterpart implemented by analog circuit design. Furthermore, AD82589 is pop free during instantaneous power switching because of its built-in, robust anti-pop circuit.

Publication Date: Apr. 2016 Revision: 0.4 1/66

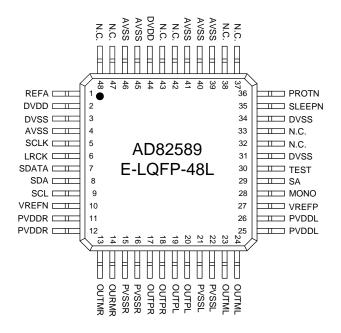

## **Pin Assignment**

## **Pin Description**

| NAME  | Pin no. | TYPE | DESCRIPTION                                                      | CHARACTERISTICS |

|-------|---------|------|------------------------------------------------------------------|-----------------|

| REFA  | 1       | 0    | 1.8V Regulator voltage output.                                   |                 |

| DVDD  | 2       | Р    | 3.3V Power supply for internal digital circuit.                  |                 |

| DVSS  | 3       | Р    | Ground terminal for internal digital circuitry.                  |                 |

| AVSS  | 4       | Р    | Ground terminal for internal analog circuitry.                   |                 |

| SCLK  | 5       | I    | Serial audio port bit clock.                                     |                 |

| LRCK  | 6       | I    | Serial audio port word clock.                                    |                 |

| SDATA | 7       | I    | Serial audio port serial data in.                                |                 |

| SDA   | 8       | I/O  | I <sup>2</sup> C data input.                                     |                 |

| SCL   | 9       | I/O  | I <sup>2</sup> C clock input.                                    |                 |

| VREFN | 10      | 0    | Low side gate drive internal regulator output.                   |                 |

| PVDDR | 11      | Р    | RCH power supply for power stage.                                |                 |

| PVDDR | 12      | Р    | RCH power supply for power stage.                                |                 |

| OUTMR | 13      | 0    | Negative terminal for RCH differential speaker amplifier output. |                 |

| OUTMR | 14      | 0    | Negative terminal for RCH differential speaker amplifier output. |                 |

| PVSSR | 15      | Р    | RCH ground for power stage.                                      |                 |

| PVSSR | 16      | Р    | RCH ground for power stage.                                      |                 |

| OUTPR | 17      | 0    | Positive terminal for RCH PWM output.                            |                 |

| OUTPR | 18      | 0    | Positive terminal for RCH PWM output.                            |                 |

| OUTPL | 19      | 0    | Positive terminal for LCH PWM output.                            |                 |

| OUTPL | 20      | 0    | Positive terminal for LCH PWM output.                            |                 |

Publication Date: Apr. 2016 Revision: 0.4 2/66

| <del> </del> |    |   |                                                 |

|--------------|----|---|-------------------------------------------------|

| PVSSL        | 21 | Р | LCH ground for power stage.                     |

| PVSSL        | 22 | Р | LCH ground for power stage.                     |

| OUTML        | 23 | 0 | Negative terminal for LCH PWM output.           |

| OUTML        | 24 | 0 | Negative terminal for LCH PWM output.           |

| PVDDL        | 25 | Р | LCH power supply for power stage.               |

| PVDDL        | 26 | Р | LCH power supply for power stage.               |

| VREFP        | 27 | 0 | High side gate drive internal regulator output. |

| MONO         | 28 | I | MONO output control pin.                        |

| SA           | 29 | I | I <sup>2</sup> C address setup.                 |

| TEST         | 30 | 1 | This pin must be connected to GND.              |

| DVSS         | 31 | Р | Ground terminal for internal digital circuitry. |

| NC           | 32 | _ | No connect.                                     |

| NC           | 33 | _ | No connect.                                     |

| DVSS         | 34 | Р | Ground terminal for internal digital circuitry. |

| SLEEPN       | 35 | I | Power down control (Low for power down).        |

| PROTN        | 36 | 0 | Error indicator, Low stands for error signal.   |

| NC           | 37 | _ | No connect.                                     |

| NC           | 38 | _ | No connect.                                     |

| AVSS         | 39 | Р | Ground terminal for internal analog circuitry.  |

| AVSS         | 40 | Р | Ground terminal for internal analog circuitry.  |

| AVSS         | 41 | Р | Ground terminal for internal analog circuitry.  |

| NC           | 42 | = | No connect.                                     |

| NC           | 43 | = | No connect.                                     |

| DVDD         | 44 | Р | 3.3V Power supply for internal digital circuit. |

| AVSS         | 45 | Р | Ground terminal for internal analog circuitry.  |

| AVSS         | 46 | Р | Ground terminal for internal analog circuitry.  |

| NC           | 47 | = | No connect.                                     |

| NC           | 48 | _ | No connect.                                     |

Note:

P: Power or ground pins; I: Input pins; O: Output pins; I/O: The bidirectional pins.