# High Input Voltage, Low Quiescent Current, Low-Dropout Linear Regulator

## **General Description**

The EMP8045 is a high voltage, low quiescent current, low dropout regulator with 150mA output driving capacity. The EMP8045, which operates over an input range of 3V to 32V, is stable with any capacitors, whose capacitance is larger than  $1\mu\text{F},$  and suitable for powering battery-management ICs because of the virtue of its low quiescent current consumption and low dropout voltage. EMP8045 also includes bandgap voltage reference, Foldback current limiting and thermal overload protection.

## **Applications**

- Logic Supply for High Voltage Batteries

- Keep-Alive Supply

- 3-4 Cell Li-ion Batteries Powered systems

- Automotive

## **Features**

- AEC-Q100 qualified

- 150mA output current driving capacity

- 780mV typical dropout at Io=150mA@V<sub>OUT</sub>=5V

- 10µA typical quiescent current

- 1µA typical shutdown mode

- 3.0V to 32V input range

- Stable with small ceramic output capacitors (1uF)

- Over temperature and over current protection

- ±1.5% output voltage tolerance

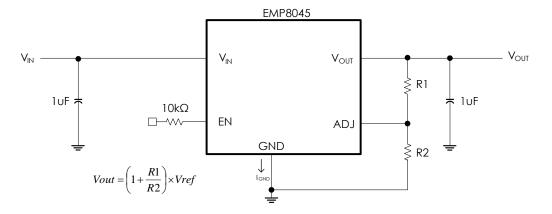

### **Typical Application**

Note: R1≥10k is strongly recommended. Especially, Vout was set around Vref

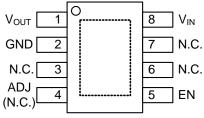

# **Connection Diagrams**

N.C.: No Connection For Fixed Vout, Pin4= No Connection

## **Order information**

EMP8045-XXSG08VCR XX Output voltage SG08 E-SOP-8 Package

VCR RoHS & Halogen free package Rating: -40 to 125°C Package in Tape & Reel

# Order, Marking & Packing Information

Elite Semiconductor Memory Technology Inc.

| Package  | Vout | Product ID.        | Marking          | Packing              |

|----------|------|--------------------|------------------|----------------------|

|          | ADJ  | EMP8045-00SG08VCR  | 8 7 6 5          |                      |

| E-SOP-8L | 3.3V | EMP8045-33\$G08VCR | ESMT<br>EMP8045  | Tape & Reel<br>3kpcs |

|          | 5.0V | EMP8045-50\$G08VCR | FIN1 DOT 1 2 3 4 | Зкроз                |

## **Pin Functions**

| Pin No.              | Name           | Function                                                                           |  |  |

|----------------------|----------------|------------------------------------------------------------------------------------|--|--|

| 1                    | Vout           | Output Voltage                                                                     |  |  |

| 2                    | GND            | Fround Pin                                                                         |  |  |

| 3                    | N.C.           | No connect                                                                         |  |  |

|                      |                | Output Voltage Adjust:                                                             |  |  |

| 4                    | ADJ            | Feedback input. Connect to resistive voltage-divider network.                      |  |  |

| 4                    | (N.C.)         | R1≥10k is strongly recommended. Especially, Vout was set as Vref                   |  |  |

|                      |                | No connect for Fixed Vout.                                                         |  |  |

|                      | Shutdown Input |                                                                                    |  |  |

| 5                    | EN             | The EN pin is pulled "High" internally. Set the regulator into the disable mode by |  |  |

|                      |                | pulling the EN pin low.                                                            |  |  |

| 6                    | N.C.           | No connect                                                                         |  |  |

| 7                    | N.C.           | No connect                                                                         |  |  |

| Supply Voltage Input |                | Supply Voltage Input                                                               |  |  |

| 8                    | $V_{IN}$       | Require a minimum input capacitor of close to 1µF to ensure stability and          |  |  |

|                      |                | sufficient decoupling from the ground pin.                                         |  |  |

Revision: 1.1

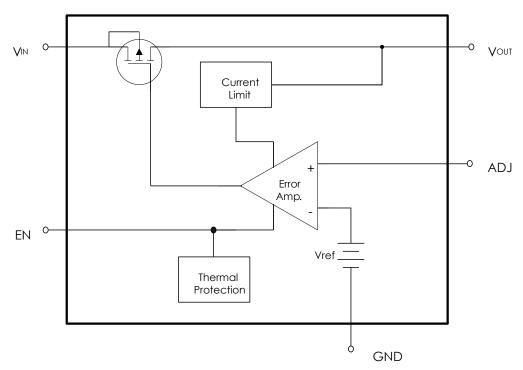

# **Functional Block Diagram**

FIG.1. Functional Block Diagram of EMP8045

Absolute Maximum Ratings (Notes 1, 2)

V<sub>IN</sub>, EN -0.3V to 36V Lead Temperature (Soldering, 10 sec.) 260°C

V<sub>OUT</sub> -0.3V to 8V ESD Rating

Power Dissipation (Note 3) Human Body Model +-2KV

Storage Temperature Range -65°C to 150°C Charged Device Model +-750V

Junction Temperature (TJ) 150°C Latch up +-100mA

Operating Ratings (Note 1, 2)

Supply Voltage 3.0V to 32V Operating Temperature Range -40°C to 125°C

#### Thermal data

| Package  | Thermal resistance               | Parameter              | Value  |

|----------|----------------------------------|------------------------|--------|

|          | θ JA (Note 4)                    | Junction-to-ambient    | 50°C/W |

| E-SOP-8L | θ JC (top) (Note 5)              | Junction-case (top)    | 39°C/W |

|          | θ <sub>JC(bottom)</sub> (Note 6) | Junction-case (bottom) | 10°C/W |

#### **Electrical Characteristics**

$V_{OUT}(NOM)=5V$ ; unless otherwise specified, all limits guaranteed for  $V_{IN}=V_{OUT}+1V$ , EN = 2V,  $C_{IN}=C_{OUT}=1\mu F$ .  $T_A=-40^{\circ}C$  to 125°C, typical value is  $T_A=+25^{\circ}C$

| Symbol              | Parameter                           | Conditions                                                                                                                                            | Min   | Typ<br>(Note7) | Max   | Units             |

|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|-------|-------------------|

|                     |                                     | $I_{OUT} = 0.1 \text{ mA}$<br>$V_{IN} = V_{OUT (NOM)} + 1 \text{ V} \le V_{IN} \le 36 \text{ V}$<br>$I_A = 25^{\circ}\text{C}$                        | 1.228 | 1.24           | 1.252 |                   |

| Vref                | Reference voltage                   | $I_{OUT} = 0.1 \text{mA}$<br>$V_{IN} = V_{OUT (NOM)} + 1 \text{V} \le V_{IN} \le 36 \text{V}$<br>$I_A = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ | 1.222 | 1.24           | 1.258 | V                 |

| TC                  | Vref temperature coefficient        | $V_{IN} = V_{OUT} + 1V$ , EN = 2V, $I_{OUT} = 0.1$ mA<br>Refer to $T_{A}$ = 25°C                                                                      | -100  | ±50            | 100   | ppm/°C            |

| Гоит                | Maximum Output Current              | Average DC Current Rating                                                                                                                             | 150   |                |       | mA                |

| I <sub>LIMIT</sub>  | Output Current Limit                | $V_{IN}$ = 6V; $T_{A}$ = -40°C ~ 125°C<br>Over-Loading                                                                                                | 180   | 240            | 300   | mA                |

| I <sub>Short</sub>  | Short Circuit Current               | $V_{IN}$ = 6V; $T_A$ = -40°C ~ 125°C<br>$V_{OUT}$ Short to GND                                                                                        | 70    | 100            | 130   | mA                |

|                     | Supply Current                      | I <sub>OUT</sub> = 0.1mA                                                                                                                              |       | 12             | 30    |                   |

| IQ                  |                                     | I <sub>OUT</sub> = 100mA                                                                                                                              |       | 50             | 100   | μA                |

|                     | Shutdown Supply Current             | V <sub>OUT</sub> = 0V, EN = GND                                                                                                                       |       | 1.5            | 5     |                   |

|                     | Dropout Voltago                     | I <sub>OUT</sub> = 30mA, T <sub>A</sub> = -40°C ~ 125°C                                                                                               |       | 135            | 250   |                   |

| $V_{\text{DO}}$     | Dropout Voltage Vout=5.0V (Note. 8) | $I_{OUT} = 100$ mA, $T_A = -40$ °C ~ 125°C                                                                                                            |       | 450            | 900   | mV                |

|                     | VOUI-3.0V (NOTE. 8)                 | I <sub>OUT</sub> = 150mA, T <sub>A</sub> = -40°C ~ 125°C                                                                                              |       | 780            | 1500  |                   |

| $\Delta V_{ m OUT}$ | Line Regulation                     | $I_{OUT} = 0.1 \text{mA}, (V_{OUT} + 1V) \le V_{IN} \le 36V$                                                                                          |       | 0.1            | 0.2   | %                 |

| ∆ v OUI             | Load Regulation                     | 0.1mA ≤ I <sub>OUT</sub> ≤ 100mA                                                                                                                      |       | 0.5            | 1     | %                 |

| <b>e</b> n          | Output Voltage Noise                | $I_{OUT}$ =10mA,10Hz $\leq$ f $\leq$ 100kHz<br>$V_{OUT}$ = 5.0V                                                                                       |       | 800            |       | μV <sub>RMS</sub> |

Publication Date: Oct. 2018 Revision: 1.1 4/13

|                 | E                                     | $V_{IH}$ , $(V_{OUT} + 1V) \le V_{IN} \le 36V$ | 1.0 |      |     |              |  |

|-----------------|---------------------------------------|------------------------------------------------|-----|------|-----|--------------|--|

| $V_{EN}$        | EN Input Threshold                    | $V_{IL}$ , $(V_{OUT} + 1V) \le V_{IN} \le 36V$ |     |      | 0.3 | V            |  |

| I <sub>EN</sub> | EN Input Bias Current                 | $EN = GND \text{ or } V_{IN} (V_{IN} < 6V)$    |     | 0.15 | 0.3 | μΑ           |  |

| +               | Thermal Shutdown Temperature(Note. 9) |                                                |     | 160  |     | 0.7          |  |

| Isd             | Thermal Shutdown Hysteresis (Note. 9) |                                                |     | 30   |     | $^{\circ}$ C |  |

| t <sub>on</sub> | Start-Up Time                         | Cout = 1.0µF, Vout at 90% of Final Value       |     | 500  |     | μs           |  |

- **Note 1:** Absolute Maximum ratings indicate limits beyond which damage may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

- Note 2: All voltages are with respect to the potential at the ground pin.

- Note 3: Maximum Power dissipation for the device is calculated using the following equations:

$$\mathsf{P}_D = \frac{\mathsf{T}_{J(\mathsf{MAX})} - \mathsf{T}_{A}}{\mathsf{\theta}_{JA}}$$

Where  $T_J(MAX)$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance. E.g. for the E-SOP-8 package  $\theta_{JA} = 50^{\circ}\text{C/W}$ ,  $T_J(MAX) = 150^{\circ}\text{C}$  and using  $T_A = 25^{\circ}\text{C}$ , the maximum power dissipation is found to be 2.5W. The derating factor  $(-1/\theta_{JA}) = -20\text{mW/°C}$ , thus below 25°C the power dissipation figure can be increased by 20mW per degree, and similarity decreased by this factor for temperatures above 25°C.

- Note 4:  $\theta$   $_{JA}$  is simulated in the natural convection at  $T_A=25^{\circ}C$  on a highly effective thermal conductivity (thermal land area completed with >3x3cm² area) board (2 layers , 2SOP ) according to the JEDEC 51-7 thermal measurement standard.

- **Note 5:**  $\theta$  <sub>JC(top)</sub> represents the heat resistance between the chip junction and the top surface of package.

- **Note 6:**  $\theta$  <sub>JC(bottom)</sub> represents the heat resistance between the chip junction and the center of the exposed pad on the underside of the package.

- Note 7: Typical Values represent the most likely parametric norm

- **Note 8:** Dropout voltage is measured by reducing V<sub>IN</sub> until V<sub>OUT</sub> drops to 98% its nominal value.

- Note 9: Design Guarantee

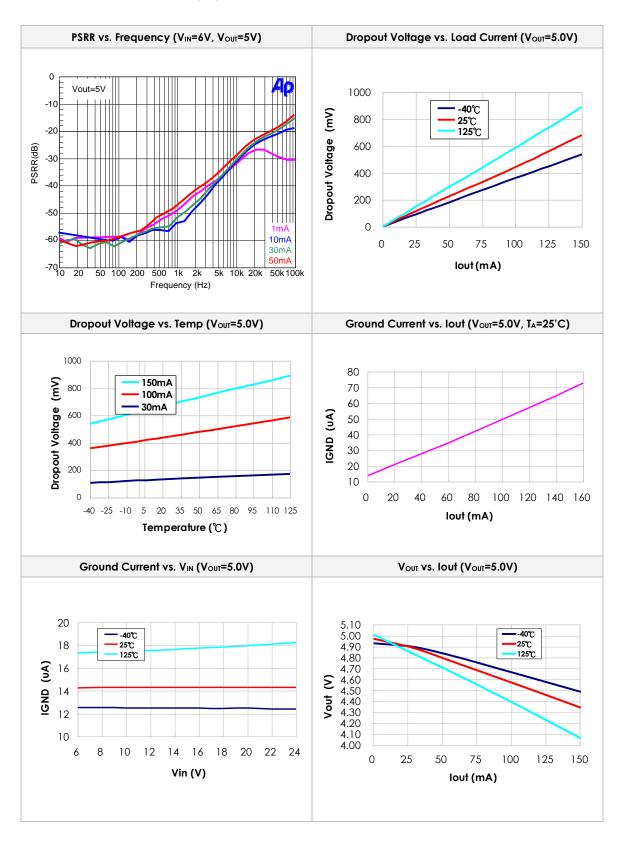

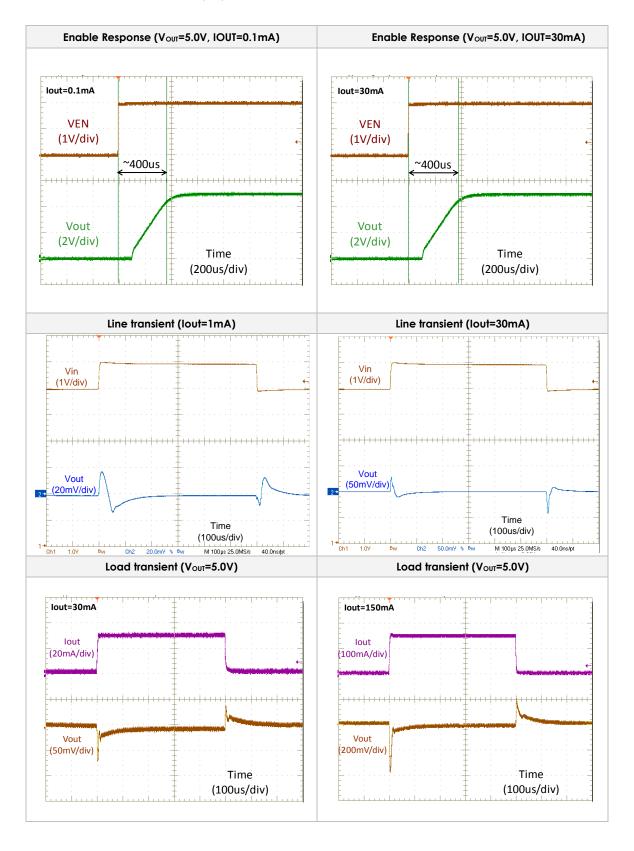

## **Typical Performance Characteristics**

Unless otherwise specified,  $V_{IN} = V_{OUT (NOM)} + 1V$ ,  $V_{OUT} = 5V$ ,  $C_{IN} = C_{OUT} = 1.0 \mu F$ ,  $T_A = 25$ °C, EN = 2V

Publication Date: Oct. 2018 Revision: 1.1 6/13

## Typical Performance Characteristics (cont.)

Unless otherwise specified,  $V_{IN} = V_{OUT (NOM)} + 1V$ ,  $V_{OUT} = 5V$ ,  $C_{IN} = C_{OUT} = 1.0 \mu F$ ,  $T_A = 25$ °C, EN = 2V

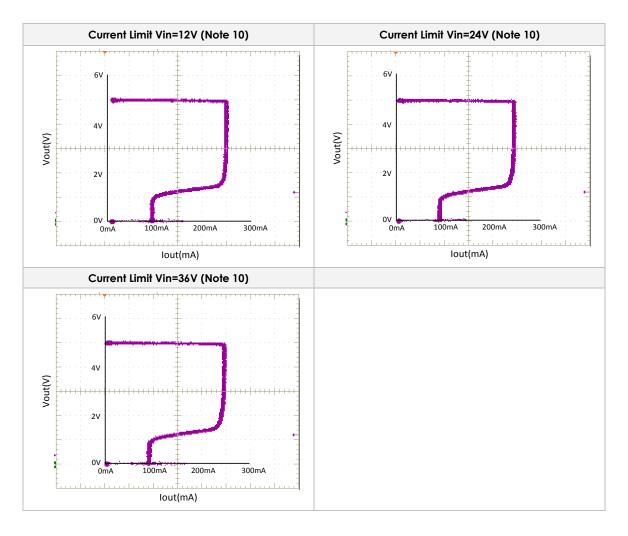

# Typical Performance Characteristics (cont.)

Unless otherwise specified,  $V_{IN} = V_{OUT (NOM)} + 1V$ ,  $V_{OUT} = 5V$ ,  $C_{IN} = C_{OUT} = 1.0 \mu F$ ,  $T_A = 25^{\circ}C$ , EN = 2V

Note 10: The Foldback current limit waveform is tested by enabling on EMP8045 with Cout=1000uF.

Publication Date: Oct. 2018 Revision: 1.1 **8/13**

#### **Application Information**

#### **General Description**

Referring to Fig.1 as shown in the Functional Block Diagram section, the EMP8045 adopts the classical regulator topology in which negative feedback control is used to perform the desired voltage regulating function. The negative feedback is formed by using feedback resistors (R1, R2) to sample the output voltage for the non-inverting input of the error amplifier, whose inverting input is set to the bandgap reference voltage. By the virtue of its high open-loop gain, the error amplifier operates to ensure that the sampled output feedback voltage at its non-inverting input is virtually equal to the preset bandgap reference voltage.

The error amplifier compares the voltage difference at its inputs and produces an appropriate driving voltage to the P-channel MOS pass transistor to control the amount of current reaching the output. If there are changes in the output voltage due to load changes, the feedback resistors register such changes to the non-inverting input of the error amplifier. The error amplifier then adjusts its driving voltage to maintain virtual short between its two input nodes under all loading conditions. In a nutshell, the regulation of the output voltage is achieved as a direct result of the error amplifier keeping its input voltages equal. This negative feedback control topology is further augmented by the shutdown, the fault detection, and the temperature and current protection circuitry. With sensing output voltage, the current limit level would be Foldback to lower level during Vout shorted to GND

#### **Output Capacitor**

The EMP8045 is specially designed for use with ceramic output capacitors of as low as 1.0 $\mu$ F to take advantage of the savings in cost and space as well as the superior filtering of high frequency noise. Capacitors of higher value or other types may be used, but it is important to make sure its equivalent series resistance (ESR) is restricted to less than  $0.5\Omega$ . The use of larger capacitors with smaller ESR values is desirable for applications involving large and fast input or output transients, as well as for situations where the application systems are not physically located immediately adjacent to the battery power source. Typical ceramic capacitors suitable for use with the EMP8045 are X5R and X7R. The X5R and the X7R capacitors are able to maintain their capacitance values to within  $\pm 20\%$  and  $\pm 10\%$ , respectively, as the temperature increases.

#### **No-Load Stability**

The EMP8045 is capable of stable operation during no-load conditions, a mandatory feature for some applications such as CMOS RAM keep-alive operations.

#### Input Capacitor

A minimum input capacitance of 1µF is required for EMP8045. The capacitor value may be increased without limit. Improper workbench set-ups may have adverse effects on the normal operation of the regulator. A case in point is the instability that may result from long supply lead inductance coupling to the output through the gate capacitance of the pass transistor. This will establish a pseudo LCR network, and is likely to happen under high current conditions or near dropout. A 10µF tantalum input capacitor will dampen the parasitic LCR action thanks to its high ESR. However, cautions should be exercised to avoid regulator short-circuit damage when tantalum capacitors are used, for they are prone to fail in short-circuit operating conditions.

Publication Date: Oct. 2018

Revision: 1.1 9/13

#### Power Dissipation and Thermal Shutdown

Thermal overload results from excessive power dissipation that causes the IC junction temperature to increase beyond a safe operating level. The EMP8045 relies on dedicated thermal shutdown circuitry to limit its total power dissipation. An IC junction temperature  $T_J$  exceeding  $150^{\circ}$ C will trigger the thermal shutdown logic, turning off the P-channel MOS pass transistor. The pass transistor turns on again after the junction cools off by about 30°C. When continuous thermal overload conditions persist, this thermal shutdown action then results in a pulsed waveform at the output of the regulator. The concept of thermal resistance  $\theta_{JA}$  (°C/W) is often used to describe an IC junction's relative readiness in allowing its thermal energy to dissipate to its ambient air. An IC junction with a low thermal resistance is preferred because it is relatively effective in dissipating its thermal energy to its ambient, thus resulting in a relatively low and desirable junction temperature. The relationship between  $\theta_{JA}$  and  $T_J$  is as follows:

$$T_J = \Theta_{JA} \times (P_D) + T_A$$

$T_A$  is the ambient temperature, and  $P_D$  is the power generated by the IC and can be written as:

As the above equations show, it is desirable to work with ICs whose  $\theta_{JA}$  values are small such that  $T_J$  does not increase strongly with  $P_D$ . To avoid thermally overloading the EMP8045, refrain from exceeding the absolute maximum junction temperature rating of 150°C under continuous operating conditions. Overstressing the regulator with high loading currents and elevated input-to-output differential voltages can increase the IC die temperature significantly.

#### Shutdown

The EMP8045 enters the sleep mode when the EN pin is low. When this occurs, the pass transistor, the error amplifier, and the biasing circuits, including the bandgap reference, are turned off, thus reducing the supply current to typically 1µA. Such a low supply current makes the EMP8045 best suited for battery-powered applications. The maximum guaranteed voltage at the EN pin for the sleep mode to take effect is 0.3V. The EN pin is pulled high internally.

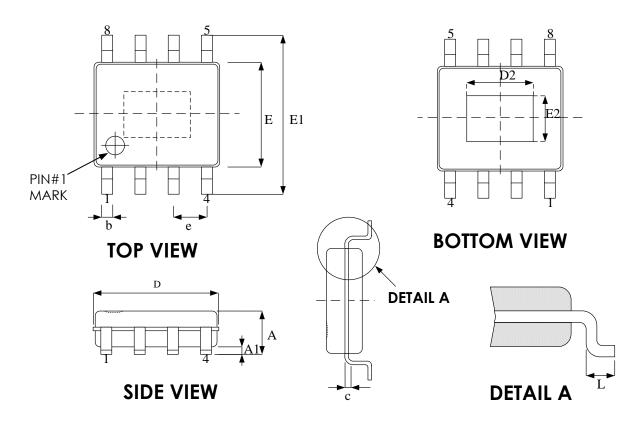

# **Package Outline Drawing** E-SOP-8

| C1 1   | Dimension in mm |      |  |

|--------|-----------------|------|--|

| Symbol | Min             | Max  |  |

| А      | 1.35            | 1.75 |  |

| A1     | 0.00            | 0.25 |  |

| Ъ      | 0.31            | 0.51 |  |

| С      | 0.10            | 0.25 |  |

| D      | 4.80            | 5.00 |  |

| Е      | 3.81            | 4.00 |  |

| E1     | 5.79            | 6.20 |  |

| е      | 1.27 BSC        |      |  |

| L      | 0.40            | 1.27 |  |

| Exposed pad |          |         |

|-------------|----------|---------|

|             | Dimensio | on in r |

|             | ) (r     | 3.7     |

|     | Dimension in mm |      |  |

|-----|-----------------|------|--|

|     | Min             | Max  |  |

| D2  | 2.84            | 3.30 |  |

| E2. | 2.06            | 2.41 |  |

# **Revision History**

| Revision | Date                                      | Description                                                                            |

|----------|-------------------------------------------|----------------------------------------------------------------------------------------|

| 0.1      | 2017.07.19 Initial version (Preliminary). |                                                                                        |

| 0.2      | 2017.08.29                                | Update application circuit                                                             |

| 0.3      | 2018.01.25                                | Update Vout max to 8V                                                                  |

| 0.4      | 2018.08.01                                | Delete 3.0V option                                                                     |

| 1.0      | 2018.09.06                                | Remove preliminary and change version to 1.0                                           |

| 1.1      | 2018.10.17                                | Modified EN pin description.     Added ESD charge device mode and latch up pass level. |

Publication Date: Oct. 2018 Revision: 1.1 12/13

# Important Notice

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Oct. 2018 Revision: 1.1 13/13