# Low EMI 2.7W Boosted Class-D Audio Power Amplifier

#### DESCRIPTION

The EUA2510A integrates a current-mode boost converter with a high efficiency mono, Class D audio power amplifier to provide 2.7W/10% THD or 2W/1% THD continuous power into a  $4\Omega$  speaker when operating on a 3.3V power supply with boost voltage (PV1) of 5V. The Class D amplifier is a low noise, filterless PWM architecture that eliminates the output filter, reducing external component count, board area consumption, system cost, and simplifying design.

The EUA2510A's boost converter, operating at a fixed frequency of 600KHz, generates a high voltage rail which is used to supply the Class-D amplifier. The EUA2510A features a low-power consumption shutdown mode. Shutdown may be enabled by driving the Shutdown pin to a logic low (GND).

The gain of the Class D is externally configurable which allows independent gain control from multiple sources by summing the signals. Output short circuit and Thermal shutdown protection prevent the device from damage during fault conditions. Superior click and pop suppression eliminates audible transients during power-up and shutdown.

#### **FEATURES**

- 2.7W/10% THD into a  $4\Omega$  Load with a 3.3V Supply

- Fully Differential Inputs

- Externally Configurable Gain on Class D

- 2.7V 5V operation (V<sub>DD</sub>)

- Independent Boost and Amplifier Shutdown Pins

- 0.5µA Shutdown Current

- Integrated Pop and Click Suppression Circuitry

- 3mm×4mm TDFN-14 Package

- RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

#### **APPLICATIONS**

- Mobile Phones

- GPS

- Portable Media

- Handheld Games

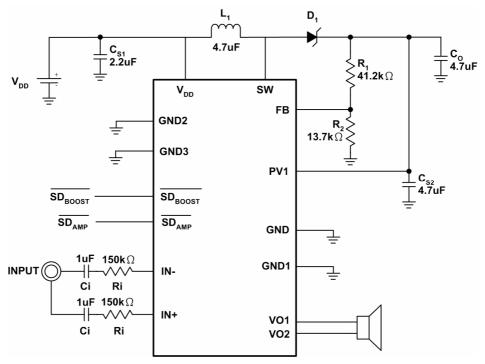

#### **Typical Application Circuit**

Figure 1.

# **Pin Configurations**

| Package Type | Pin Configurations  |     |             |      |       |

|--------------|---------------------|-----|-------------|------|-------|

|              | (TOP VIEW)          |     |             |      |       |

|              | VO1                 |     |             | [14] | GND   |

|              | GND1                | 2   |             | [13] | IN+   |

| TDFN-14      | PV1                 | [3] |             | 12   | IN-   |

|              | VO2                 | 4   | Thermal Pad | (11) | SDAMP |

|              | SD <sub>BOOST</sub> | [5] |             | [10] | VDD   |

|              | GND2                |     |             | 9    | GND3  |

|              | FB                  | 7   |             | 8    | SW    |

|              |                     |     |             |      |       |

# **Pin Description**

| PIN               | TDFN-14 | DESCRIPTION                                                 |

|-------------------|---------|-------------------------------------------------------------|

| VO1               | 1       | Amplifier Output                                            |

| GND1              | 2       | GND                                                         |

| PV1               | 3       | Amplifier Power Input                                       |

| VO2               | 4       | Amplifier Output                                            |

| SDBOOST           | 5       | Boost Regulator Active Low Shutdown                         |

| GND2              | 6       | Signal Ground (Booster)                                     |

| FB                | 7       | Feedback point that connects to external resistive divider. |

| SW                | 8       | Drain of the Internal FET Switch                            |

| GND3              | 9       | Power Ground (Booster)                                      |

| VDD               | 10      | Power Supply                                                |

| SD <sub>AMP</sub> | 11      | Amplifier Active Low Shutdown                               |

| IN-               | 12      | Amplifier Inverting Input                                   |

| IN+               | 13      | Amplifier Non-Inverting Input                               |

| GND               | 14      | GND                                                         |

DS2510A Ver1.0 Apr. 2010

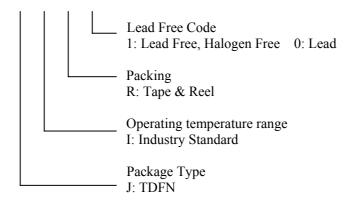

# **Ordering Information**

| Order Number | Package Type Marking |                | Operating Temperature Range |

|--------------|----------------------|----------------|-----------------------------|

| EUA2510AJIR1 | TDFN-14              | xxxxx<br>2510A | -40 °C to 85°C              |

#### EUA2510A

## **Absolute Maximum Ratings**

| Supply Voltage, V <sub>DD</sub>            | 6V                   |

|--------------------------------------------|----------------------|

| Input Voltage                              | -0.3 V to VINA +0.3V |

| Junction Temperature Range, T <sub>J</sub> | 150°C                |

| Storage Temperature Rang, T <sub>stg</sub> | 65°C to 150°C        |

| ESD Susceptibility                         | 2kV                  |

| Thermal Resistance                         |                      |

| θια (TDFN)                                 | 47°C/W               |

## **Recommended Operating Conditions**

|                                                | Min | Max | Unit |

|------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>DD</sub>                | 2.7 | 5   | V    |

| Operating free-air temperature, T <sub>A</sub> | -40 | 85  | °C   |

Electrical Characteristics  $V_{DD}$ =3.3V The following specifications apply for  $V_{DD}$  =3.3V,PV<sub>1</sub>=5V,A<sub>V</sub>=6dB (R<sub>i</sub>=150k $\Omega$ ), R<sub>L</sub>=15 $\mu$ H+8 $\Omega$ +15 $\mu$ H ,f<sub>IN</sub>=1kHz, unless otherwise specified. Limits apply for T<sub>A</sub>=25°C.

| Cross b ol          | Parameter                         | C142                                                                                        | EUA2510A   |                   |              | Unit          |

|---------------------|-----------------------------------|---------------------------------------------------------------------------------------------|------------|-------------------|--------------|---------------|

| Symbol              |                                   | Conditions                                                                                  | Min.       | Typ.              | Max.         | UIII          |

| $I_{DD}$            | Quiescent Power Supply<br>Current | $V_{IN}=0, R_{LOAD}=\infty$                                                                 |            | 7.6               |              | mA            |

| $I_{(SD)}$          | Shutdown Current                  | $\overline{\text{(SD - AMP)}} = \overline{\text{(SD - BOOST)}} = GND$                       |            | 1                 |              | μΑ            |

| $V_{\mathrm{SDIH}}$ | Shutdown Voltage Input<br>High    | (SD - AMP)<br>(SD - BOOST)                                                                  | 1.3<br>1.3 |                   |              | V<br>V        |

| $V_{ m SDIL}$       | Shutdown Voltage Input<br>Low     | (SD - BOOST)<br>(SD - AMP)                                                                  |            |                   | 0.35<br>0.35 | V<br>V        |

| $T_{ m WU}$         | Wake-up Time                      |                                                                                             |            | 11.4              |              | ms            |

| VOS                 | Output Offset Voltage             |                                                                                             |            | 4                 |              | mV            |

|                     | Output Power                      | $R_L$ =15 $\mu$ H+4 $\Omega$ +15 $\mu$ H ,THD+N=1% (max),<br>f=1kHz,22kHz,BW $V_{DD}$ =3.3V |            | 2                 |              | W             |

|                     |                                   | $R_L$ =15 $\mu$ H+8 $\Omega$ +15 $\mu$ H ,THD+N=1% (max),<br>f=1kHz,22kHz,BW $V_{DD}$ =3.3V |            | 1.2               |              |               |

|                     |                                   | $R_L$ =15 $\mu$ H+4 $\Omega$ +15 $\mu$ H,THD+N=10%(max),<br>f=1kHz,22kHz,BW                 |            |                   |              |               |

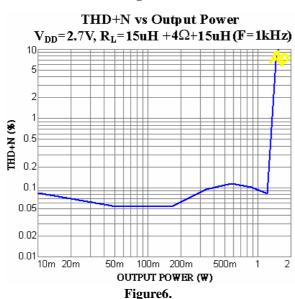

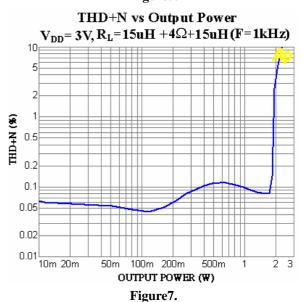

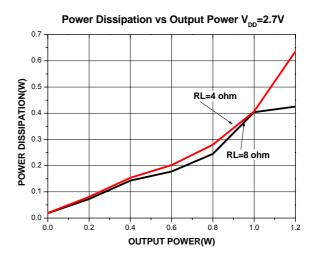

| P <sub>O</sub>      |                                   | $V_{DD}$ =2.7V<br>$V_{DD}$ =3V<br>$V_{DD}$ =3.3V                                            |            | 1.5<br>2.1<br>2.7 |              |               |

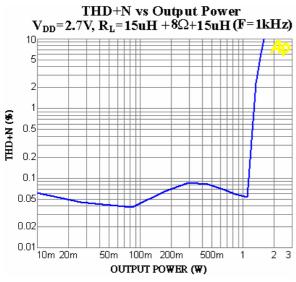

|                     |                                   | $R_L=15\mu H+8\Omega+15\mu H, THD+N=10\%(max), f=1kHz, 22kHz, BW V_{DD}=2.7V$               |            | 1.6               |              |               |

|                     |                                   | $V_{DD}=2.7V$<br>$V_{DD}=3.3V$                                                              |            | 1.6               |              |               |

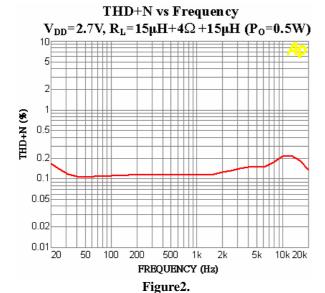

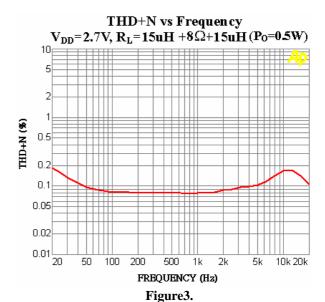

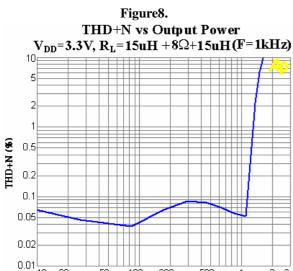

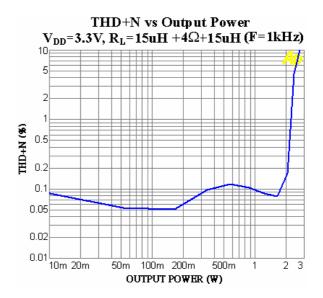

| THD+N               | Total Harmonic Distortion         | Po=500mW, f=1kHz, R <sub>L</sub> =15μH+8Ω+15μH $V_{DD}$ =2.7V                               |            | 0.081             |              | %             |

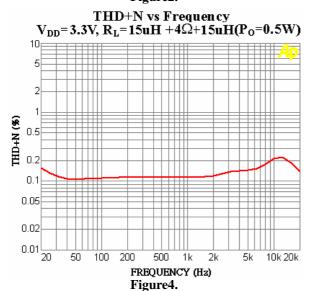

| I HD+N              | + Noise                           | Po=500mW, f=1kHz, $R_L$ =15μH+8Ω+15μH $V_{DD}$ =3.3V                                        |            | 0.068             |              | %             |

|                     | Output Noise                      | V <sub>DD</sub> =3.3V,f=20Hz~20kHz<br>Inputs to AC GND, No weighting<br>input referred      |            | 46                |              | $\mu V_{RMS}$ |

| $\epsilon_{ m OS}$  |                                   | V <sub>DD</sub> =3.3V,f=20Hz~20kHz<br>Inputs to AC GND, A weighting<br>input referred       |            | 27                |              | $\mu V_{RMS}$ |

# Electrical Characteristics $V_{DD}=3.3V$

The following specifications apply for  $V_{DD}$  =3.3V,PV1=5V,Av=6dB (Ri=150k $\Omega$ ), RL=15 $\mu$ H+8 $\Omega$ +15 $\mu$ H ,f<sub>IN</sub>=1kHz, unless otherwise specified. Limits apply for TA=25°C.

| Crombal    | Domomoton                           | Conditions                                                             | EUA2510A |                   |      | I In:4 |

|------------|-------------------------------------|------------------------------------------------------------------------|----------|-------------------|------|--------|

| Symbol     | Parameter                           | Conditions                                                             | Min.     | Typ.              | Max. | Unit   |

| $A_{ m V}$ | Gain                                |                                                                        |          | $300~k\Omega$ /Ri |      | V/V    |

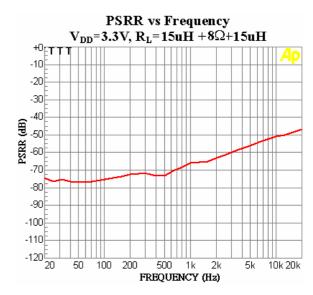

|            |                                     | $V_{RIPPLE}$ =200m $V_{P-P}$ Sine<br>f= $_{RIPPLE}$ =217Hz             |          | -75.4             |      | dB     |

| PSRR       | Power Supply Rejection Ratio        | $V_{RIPPLE}$ =200m $V_{P-P}$ Sine $f$ = $_{RIPPLE}$ =1Hz               |          | -68               |      | dB     |

|            |                                     | $V_{RIPPLE}$ =200m $V_{P-P}$ Sine<br>f= $_{RIPPLE}$ =10Hz              |          | -51               |      | dB     |

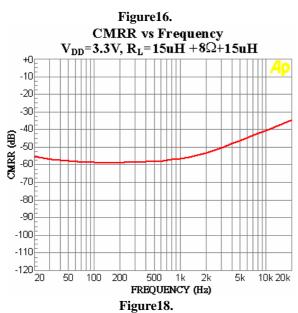

| CMRR       | Common Mode Rejection<br>Ratio      | V <sub>RIPPLE</sub> =200mV <sub>P-P,</sub> f= <sub>RIPPLE</sub> =217Hz |          | -52               |      | dB     |

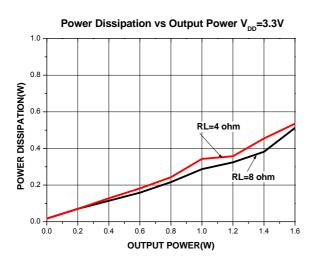

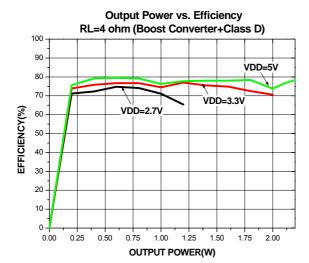

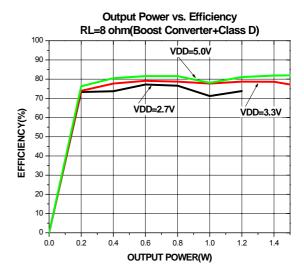

| η          | Efficiency                          | PO=1W, f=1kHz, $R_L$ =15μH+8Ω+15μH $V_{DD}$ =3.3V                      |          | 77                |      | %      |

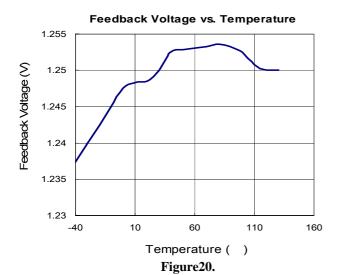

| $V_{FB}$   | FB Regulation Voltage               |                                                                        | 1.20     | 1.25              | 1.30 | V      |

|            | Boost Converter Switching Frequency |                                                                        | 450      | 600               | 750  | kHz    |

|            | Class D Switching Frequency         |                                                                        | 200      | 250               | 300  | kHz    |

| UVLO       | Under Voltage Lockout               |                                                                        | 2.2      | 2.4               | 2.6  | V      |

| $I_{OL}$   | Output Current Limit                |                                                                        | 1700     | 2200              | 2700 | mA     |

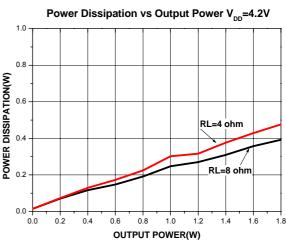

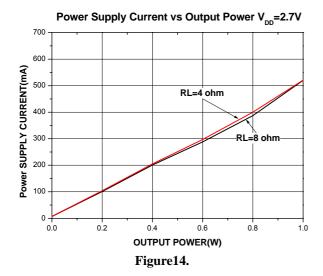

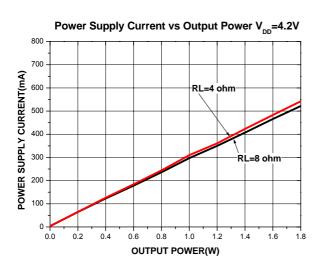

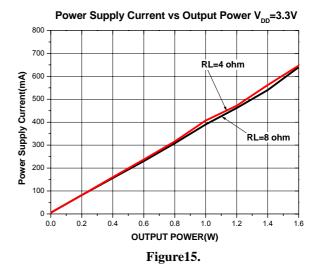

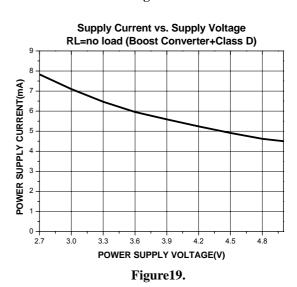

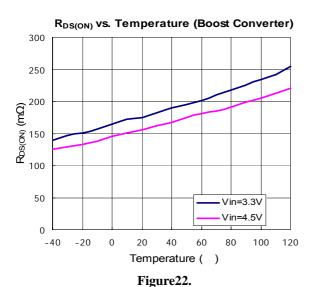

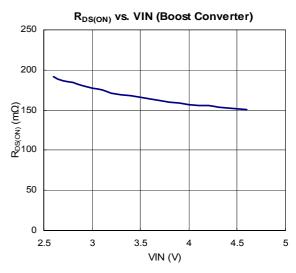

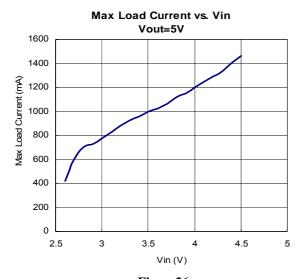

## **Typical Operating Characteristics**

100m 200m

Figure 10.

OUTPUT POWER (W)

500m

2 3

50m

Figure 12.

Figure9.

Figure 11.

Figure 13.

10m 20m

Figure 17.

#### Switching Duty Cycle vs. Temperature 73.4 73.2 Duty Cycle (%) 73 72.8 72.6 72.4 Vin=3.3V 72.2 Vin=4.5V 72 -40 -10 110 140 Temperature ( )

Figure21.

Figure 23.

Figure 25.

Figure 26.

#### **Application Information** Fully Differential Amplifier

The EUA2510A integrates a boost converter with a high efficiency mono, class-D audio power amplifier. The fully differential amplifier consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is biased around  $V_{\rm DD}/2$  regardless of the common-mode voltage at the input. The fully differential class-D can still be used with a single-ended input; however, the class-D should be used with differential inputs when in a noisy environment, like a wireless handset, to ensure maximum noise rejection.

#### **Operating Ratings**

The boost converter takes a low supply voltage (VDD), and increase it to a higher output voltage (PV1). PV1 is the power supply for the Class D amplifier. The Class D amplifier operating rating is  $2.5V \le (PV1) \le 5.5V$  when being used without the Boost. Note the output voltage (PV1) has to be more than VDD.

#### **Setting the Boost**

#### **Output Voltage**

An external feedback resistor divider is required to divide the output voltage down to the nominal 1.25V reference voltage. The current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. Selecting  $R_2$  in the range of  $10k\Omega$  to  $50~k\Omega$ . The boost converter output voltage's determined by the relationship:

$$V_{OUT} = V_{FB} \times \left[ 1 + \frac{R_1}{R_2} \right]$$

The nominal VFB voltage is 1.25V

#### **Inductor Selection**

The inductor selection determines the output ripple voltage, transient response, output current capability, and efficiency. Its selection depends on the input voltage, output voltage, switching frequency, and maximum output current. For most applications, a  $4.7\mu H$  inductor is recommended for 600 KHz. The inductor maximum DC current specification must be greater than the peak inductor current required by the regulator. The peak inductor current can be calculated:

$$I_{L(PEAK)} = \frac{I_{OUT} \times V_{OUT}}{V_{IN}} + 1/2 \times \frac{V_{IN} \times (V_{OUT} - V_{IN})}{L \times V_{OUT} \times FREQ}$$

#### **Output Capacitor**

Low ESR capacitors should be used to minimized the output voltage ripple. Multilayer ceramic capacitors (X5R and X7R) are preferred for the output capacitors because of their lower ESR and small packages. Tantalum capacitors with higher ESR can also be used. The output ripple can be calculated as:

$$\Delta V_{O} = \frac{I_{OUT} \times D}{F_{SW} \times C} + I_{OUT} \times ESR$$

Choose an output capacitor to satisfy the output ripple and load transient requirement. A  $4.7\mu F$  to  $10\mu F$  ceramic capacitor is suitable for most application.

#### **Schottky Diode**

In selecting the Schottky diode, the reverse break down voltage, forward current and forward voltage drop must be considered for optimum converter performance. The diode must be rated to handle 2A, the current limit of the EUA2510A. The breakdown voltage must exceed the maximum output voltage. Low forward voltage drop, low leakage current, and fast reverse recovery will help the converter to achieve the maximum efficiency.

### **Selecting Input Capacitor (CS1) for Boost**

#### Converter

An input capacitor is required to serve as an energy reservoir for the current which must flow into the coil each time the switch turns ON. This capacitor must have extremely low ESR, so ceramic is the best choice. A nominal value of  $4.7\mu F$  is recommended, but larger values can be used. Since this capacitor reduces the amount of voltage ripple seen at the input pin, it also reduces the amount of EMI passed back along that line to other circuitry.

#### **Maximum Output Current**

The output current capability of the EUA2510A is a function of current limit, input voltage, operating frequency, and inductor value. The output current capability is governed by the following equation:

$$I_{L} = I_{L-AVG} + (1/2 \times \Delta I_{L})$$

Where:

IL=MOSET current limit

$I_{L-AVG}$  =average inductor current

$\Delta I_{\rm I}$  =inductor ripple current

$$\Delta I_{L} = \frac{V_{IN} \times \left[ \left( V_{O} + V_{DIODE} - V_{IN} \right) - V_{IN} \right]}{L \times \left( V_{O} + V_{DIODE} \right) \times F_{S}}$$

VDIODE = Schottky diode forward voltage, typically, 0.6V

FS = switching frequency, 600KHz.

$$I_{L-AVG} = \frac{I_{OUT}}{1-D}$$

D = MOSFET turn-on ratio:

$$D = 1 - \frac{V_{IN}}{V_{OUT} + V_{DIODE}}$$

#### **Class D Requirements**

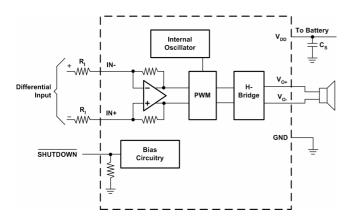

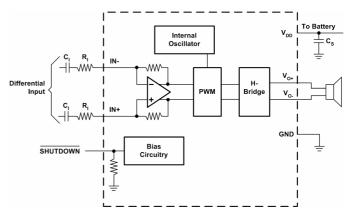

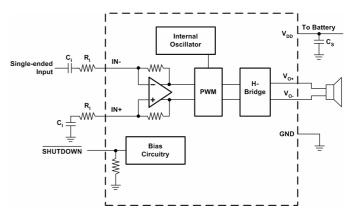

Figure 27 shows the class-D typical schematic with differential inputs and Figure 28 shows the class-D with differential inputs and input capacitors, and Figure 29 shows the class-D with single-ended inputs. Differential inputs should be used whenever possible because the single-ended inputs are much more susceptible to noise.

Table 1. Typical Component Values

| REF DES     | VALUE                          |

|-------------|--------------------------------|

| $R_{\rm I}$ | $150$ k $\Omega$ ( $\pm$ 0.5%) |

| $C_{S}$     | 1μF (+22%,-80%)                |

| $C_{I}(1)$  | 3.3nF (± 10%)                  |

(1)  $C_I$  is only needed for single-ended input or if  $V_{ICM}$  is not between 0.5 V and  $V_{DD}-0.8$  V.  $C_I=3.3$  nF (with  $R_I=150$  k $\Omega$ ) gives a high-pass corner frequency of 321 Hz.

Figure 27. Typical Application Schematic With Differential Input for a Wireless Phone

Figure 28. Typical Application Schematic With Differential Input and Input Capacitors

Figure 29. Typical Application Schematic With Single-Ended Input

#### Input Resistors (R<sub>I</sub>)

The input resistors  $(R_I)$  set the gain of the amplifier according to equation (1).

$$Gain = \frac{2 \times 150 k\Omega}{R_{I}} \quad \left(\frac{V}{V}\right) \quad -----(1)$$

Resistor matching is very important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and cancellation of the second harmonic distortion diminish if resistor mismatch occurs. Therefore, it is recommended to use 1% tolerance resistors or better to keep the performance optimized. Matching is more important than overall tolerance. Resistor arrays with 1% matching can be used with a tolerance greater than 1%.

Place the input resistors very close to the class-D to limit noise injection on the high-impedance nodes.

For optimal performance the gain should be set to 2 V/V or lower. Lower gain allows the class-D to operate at its best, and keeps a high voltage at the input making the inputs less susceptible to noise.

#### **Decoupling Capacitor (C<sub>S</sub>)**

The EUA2510A is a high-performance class-D audio amplifier with boost converter that requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD) is low. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 1 µF, placed as close as possible to the device V<sub>DD</sub> lead works best. Placing this decoupling capacitor close to the EUA2510A is very important for the efficiency of the class-D amplifier, because any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency. For filtering lower-frequency noise signals, a 10µF or greater capacitor placed near the audio power amplifier would also help, but it is not required in most applications because of the high PSRR of this device.

#### Input Capacitors (C<sub>I</sub>)

The class-D does not require input coupling capacitors if the design uses a differential source that is biased from 0.5 V to  $V_{DD}-0.8$  V (shown in Figure 27). If the input signal is not biased within the recommended common—mode input range, if needing to use the input as a high pass filter (shown in Figure 28), or if using a single-ended source (shown in Figure 29), input coupling capacitors are required.

The input capacitors and input resistors form a high-pass filter with the corner frequency, fc, determined in equation (2)

$$f_{c} = \frac{1}{\left(2\pi R_{I}C_{I}\right)} \qquad (2)$$

The value of the input capacitor is important to consider as it directly affects the bass (low frequency) performance of the circuit. Speakers in wireless phones cannot usually respond well to low frequencies, so the corner frequency can be set to block low frequencies in this application.

Equation (3) is reconfigured to solve for the input coupling capacitance.

$$C_{I} = \frac{1}{\left(2\pi R_{I} f_{c}\right)} \qquad (3)$$

If the corner frequency is within the audio band, the capacitors should have a tolerance of  $\pm 10\%$  or better, because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.

For a flat low-frequency response, use large input coupling capacitors (1  $\mu F).$  However, in a GSM phone the ground signal is fluctuating at 217 Hz, but the signal from the codec does not have the same 217 Hz fluctuation. The difference between the two signals is amplified, sent to the speaker, and heard as a 217 Hz hum.

#### **Layout Considerations**

For high frequency boost converter, it requires very careful layout of components in order to get stable operation, low noise and good regulation. Some guidelines are recommended: Place power components as close together as possible, keeping their traces short, direct, and wide. Avoid interconnecting the ground pins of the power components using vias through an internal ground plane. Instead, keep the power components close together and route them in a "star" ground configuration using component-side coper, then connect the star ground to internal ground using multiple vias.

For Class-D amplifier, to maintain the highest output voltage swing and corresponding peak output power, the PCB traces that connect the output pins to the load and the supply pins to the power supply should be as wide as possible to minimize trace resistance.

The use of power and ground planes will give the best THD+N performance. While reducing trace resistance, the use of power planes also creates parasite capacitors that help to filter the power supply line.

The inductive nature of the transducer load can also result in overshoot on one or both edges, clamped by the parasitic diodes to GND and  $V_{DD}$  in each case. From an EMI stand- point, this is an aggressive waveform that can radiate or conduct to other components in the system and cause interference. It is essential to keep the power and output traces short and well shielded if possible. Use of ground planes, beads, and micro-strip layout techniques are all useful in preventing unwanted interference.

As the distance from the EUA2510A and the speaker increase, the amount of EMI radiation will increase since the output wires or traces acting as antenna become more efficient with length. What is acceptable EMI is highly application specific. Ferrite chip inductors placed close to the EUA2510A may be needed to reduce EMI radiation. The value of the ferrite chip is very application specific.

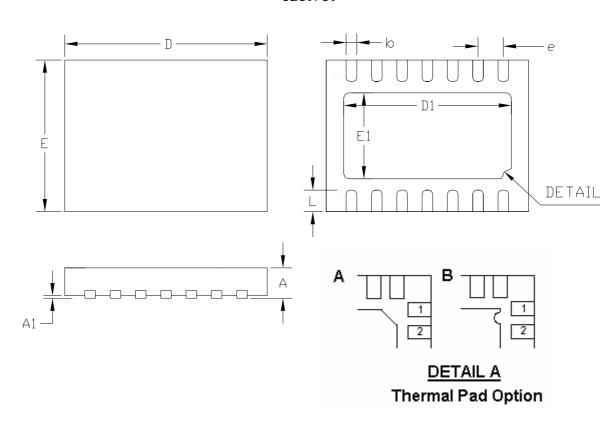

# **Package Information**

TDFN-14

| SYMBOLS  | MILLIMETERS |      | INCHES      |       |  |

|----------|-------------|------|-------------|-------|--|

| STNIBOLS | MIN.        | MAX. | MIN.        | MAX.  |  |

| A        | 0.70        | 0.80 | 0.028       | 0.031 |  |

| A1       | 0.00        | 0.05 | 0.000       | 0.002 |  |

| b        | 0.20        | 0.35 | 0.008       | 0.014 |  |

| Е        | 2.90        | 3.10 | 0.114       | 0.122 |  |

| D        | 3.90        | 4.10 | 0.153       | 0.161 |  |

| D1       | 3.25        |      | 0.128       |       |  |

| E1       | 1.65        |      | 0.065       |       |  |

| e        | 0.50        |      | 0.02        | 20    |  |

| L        | 0.30        | 0.50 | 0.012 0.020 |       |  |