# **SPE0581**

# **Ultra Low Capacitance 4 -Line ESD Protection Array**

### DESCRIPTION

The SPE0581 is 4-channel very low capacitance ESD transient voltage suppressor which provides a very high level of protection for sensitive electronic components that may be subjected to electrostatic discharge. It is particularly well-suited to protect systems with high speed communication lines from ESD, EFT, and lighting.

The SPE0581 consists of eight low capacitance steering diodes and a TVS diode in a SLP package. Each channel of SPE0581 could safely dissipate ESD strikes of  $\pm 15$ KV air discharge as well as  $\pm 8$ KV contact discharge, meeting the requirement of the IEC 61000-4-2 international standard. Using the MIL-STD-883 (Method 3015) specification for Human Body Model (HBM) ESD, the device provides protection for contact discharges to greater than  $\pm 8$ KV.

### FEATURES

• Transient protection for data lines to

IEC 61000-4-2 (ESD) ±15kV (air) ±8kV (contact)

IEC 61000-4-4 (EFT) 40A (5/50ns)

- Protects five bidirectional I/O lines

- ♦ Working voltage: 5V

- Low leakage current

- Low operating and clamping voltages

- Low capacitance: 0.3 pF typical

#### APPLICATIONS

- Cellular Handsets and Accessories

- Cordless Phone

- ♦ PDA

- Notebooks and Handhelds

- Portable Instrumentation

- Digital Cameras

- MP3 Player High Definition Multi-Media Interface Protection

- ♦ HDMI 1.2~2.1

- USB2.0/USB3.0 and Type C

- Monitors and Notebook Computers

- ♦ HDSL, IDSL Secondary IC Side Protection

- 10/100/1000 Ethernet

#### PIN CONFIGURATION (DFN-10)

#### PART MARKING

W=Specific Device Code YW =Date Code (y=year,w=week)

# **SPE0581**

# **Ultra Low Capacitance 4 -Line ESD Protection Array**

| <b>ORDERING INFORMATION</b> |  |

|-----------------------------|--|

|                             |  |

| Part Number     | Package | Part Marking |

|-----------------|---------|--------------|

| SPE0581DFN10RGB | DFN-10  | WYW          |

YW = Date Code ( $Y : 0 \sim 9$ ,  $W : A \sim Z$  and  $a \sim z$ )

SPE0581DFN10RGB : Tape Reel ; Pb – Free ; Halogen – Free

# ABSOULTE MAXIMUM RATINGS

(TA=25°C Unless otherwise noted)

| Parameter                                          | Symbol | Typical       | Unit |

|----------------------------------------------------|--------|---------------|------|

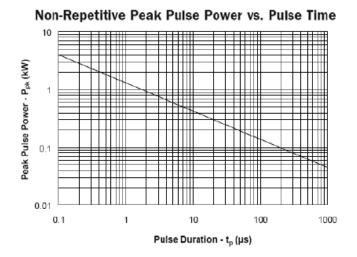

| Peak Pulse Power ( $tp = 8/20 \ \mu s$ )           | Ppk    | 60            | W    |

| Maximum Peak Pulse Current ( $tp = 8/20 \ \mu s$ ) | Ipp    | 4             | А    |

| ESD per IEC 61000 – 4 – 2 (Air )                   | Vpp    | ±15           | KV   |

| ESD per IEC 61000 – 4 – 2 (Contact )               | Vpp    | $\pm 8$       | KV   |

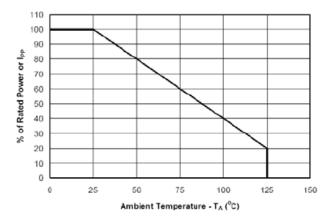

| Operating Junction Temperature                     | TJ     | -55 ~ 125     | °C   |

| Storage Temperature Range                          | Tstg   | -55 ~ 150     | °C   |

| Lead Soldering Temperature                         | TL     | 260 ( 10sec ) | °C   |

# ELECTRICAL CHARACTERISTICS

(TA=25°C Unless otherwise noted)

| Parameter                   | Symbol | Conditions                                        | Min. | Тур  | Max. | Unit |

|-----------------------------|--------|---------------------------------------------------|------|------|------|------|

| Reverse Stand – Off Voltage | Vrwm   |                                                   |      |      | 5    | V    |

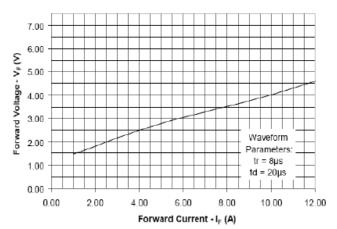

| Forward Voltage @ IF        | VF     | IF = 10mA                                         | 0.45 | 0.86 | 1.2  | V    |

| Reverse Breakdown Voltage   | Vbr    | It = 1 mA                                         | 6.0  | 7.5  |      | V    |

| Reverse Leakage Current     | Ir     | $V_{RWM} = 5V$ , T=25°C                           |      | 0.02 | 1    | μΑ   |

| Clamping Voltage            | Vc     | $Ipp = 1A$ , $tp = 8/20 \ \mu s$                  |      |      | 12   | V    |

| Innation Consoltance        | Ci     | $V_R = 0V$ , f = 1MHz<br>Any I/O pin to Ground    |      | 0.5  | 0.7  | πE   |

| Junction Capacitance        | Cj     | V <sub>R</sub> = 0V, f = 1MHz<br>Between I/O pins |      | 0.3  |      | pF   |

SPE0581 Ultra Low Capacitance 4 -Line ESD Protection Array

## **TYPICAL CHARACTERISTICS**

### **Power Derating Curve**

Clamping Voltage vs. Peak Pulse Current 40 35 Clamping Voltage -V<sub>C</sub> (V) 30 25 20 15 Waveform 10 Parameters: tr = 8µs 5 td = 20µs 0 σ 1 2 3 4 5 6 Peak Pulse Current - I<sub>FF</sub> (A)

Forward Voltage vs. Forward Current

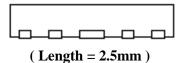

# **SCHEMATIC & PIN CONFIGURATION**

As Figure Shown is an example of how to route the high speed differential traces through the SPE0581. The solid line represents the PCB trace. The PCB traces are used to connect the pin pairs for each line (pin 1 to pin 10, pin 2 to pin 9, pin 4 to pin 7, pin 5 to pin 6). For example, line 1 enters at pin 1 and exits at Pin 10 and the PCB trace connects pin 1 and 10 together. This is true for lines connected at pins2, 4, and 5 also. Ground is connected at pins3 and 8. One large ground pad should be used in lieu of two separate pads.

Flow through Layout Using SPE0581

### APPLICATION INFORMATION ( Design Recommendations for HDMI Protection )

Adding external ESD protection to HDMI ports can be challenging. First, ESD protection devices have an inherent junction capacitance. However, adding even a small amount of capacitance will cause the impedance of the differential pair to drop. Second , large packages and land pattern requirements cause discontinuities that adversely affect signal integrity. The SPE0581 is specifically designed for protection of high-speed interfaces such as HDMI. They present <0.35pF capacitance between the pairs while being rated to handle +/-8KV ESD contact discharges (15KVair discharge) as outlined in IEC61000-4-2. Each device is in a leadless DFN package that is less than 1.1mm wide. They are designed such that the traces flow straight through the device. The narrow package and flow-through design reduces discontinuities and minimizes impact on signal integrity. This becomes even more critical as signal speed increased.

**SPE0581**

**Ultra Low Capacitance 4 -Line ESD Protection Array**

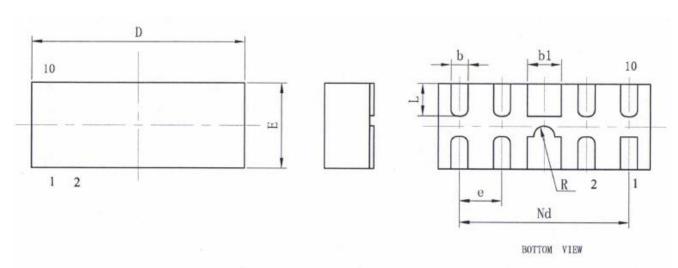

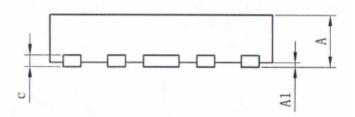

# DFN-10 PACKAGE OUTLINE

| SYMBOL           | MILLIMETER |       |       |  |

|------------------|------------|-------|-------|--|

| SIMBOL           | MIN        | NOM   | MAX   |  |

| А                | 0.45       | 0.50  | 0.55  |  |

| A1               | -          | 0.02  | 0.05  |  |

| b                | 0.15       | 0.20  | 0.25  |  |

| <b>b</b> 1       | 0.35       | 0.40  | 0.45  |  |

| с                | 0.10       | 0.15  | 0.20  |  |

| D                | 2.40       | 2.50  | 2.60  |  |

| e                | 0. 50BSC   |       |       |  |

| Nd               | 2.00BSC    |       |       |  |

| Е                | 0.90       | 1.00  | 1.10  |  |

| L                | 0.30       | 0.38  | 0.425 |  |

| R                | 0.12       | 0.125 | 0.13  |  |

| L/F载体尺寸<br>(nil) | 22X30      |       |       |  |

Information provided is alleged to be exact and consistent. SYNC Power Corporation presumes no responsibility for the penalties of use of such information or for any violation of patents or other rights of third parties which may result from its use. No license is granted by allegation or otherwise under any patent or patent rights of SYNC Power Corporation. Conditions mentioned in this publication are subject to change without notice. This publication surpasses and replaces all information previously supplied. SYNC Power Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of SYNC Power Corporation.

© The SYNC Power logo is a registered trademark of SYNC Power Corporation © 2017 SYNC Power Corporation – Printed in Taiwan – All Rights Reserved SYNC Power Corporation 7F-2, No.3-1, Park Street NanKang District (NKSP), Taipei, Taiwan, 115, R.O.C Phone: 886-2-2655-8178 Fax: 886-2-2655-8468 © http://www.syncpower.com